NXP Jun 26, 2025

# **Table of contents**

| 1 | IMX    | 943EVK 3                                             |

|---|--------|------------------------------------------------------|

|   | 1.1    | Overview                                             |

|   | 1.2    | Getting Started with MCUXpresso SDK Package          |

|   |        | 1.2.1 Getting Started with Package 3                 |

|   | 1.3    | Getting Started with MCUXpresso SDK GitHub           |

|   |        | 1.3.1 Getting Started with MCUXpresso SDK Repository |

|   | 1.4    | Release Notes                                        |

|   |        | 1.4.1 MCUXpresso SDK Release Notes                   |

|   | 1.5    | ChangeLog                                            |

|   |        | 1.5.1 MCUXpresso SDK Changelog                       |

|   | 1.6    | Driver API Reference Manual                          |

|   | 1.7    | Middleware Documentation                             |

|   |        | 1.7.1 Multicore                                      |

|   |        | 1.7.2 FreeMASTER                                     |

|   |        | 1.7.3 FreeRTOS                                       |

|   |        | 1.7.4 lwIP                                           |

|   |        |                                                      |

| 2 | Driv   |                                                      |

|   | 2.1    | DSC                                                  |

|   | 2.2    | i.MX                                                 |

|   | 2.3    | i.MX RT                                              |

|   | 2.4    | Kinetis                                              |

|   | 2.5    | LPC                                                  |

|   | 2.6    | MCX                                                  |

|   | 2.7    | Wireless                                             |

| • | 3.61.3 | 107                                                  |

| 3 |        | dleware       127         Motor Control       127    |

|   | 3.1    |                                                      |

|   |        | 3.1.1 FreeMASTER                                     |

| 4 | RTO    | S 165                                                |

| 1 | 4.1    | FreeRTOS                                             |

|   |        | 4.1.1 FreeRTOS kernel                                |

|   |        | 4.1.2 FreeRTOS drivers                               |

|   |        | 4.1.3 backoffalgorithm                               |

|   |        | 4.1.4 corehttp                                       |

|   |        | 4.1.5 corejson                                       |

|   |        | 4.1.6 coremgtt                                       |

|   |        | 4.1.7 coremqtt-agent                                 |

|   |        | 4.1.8 corepkcs11                                     |

|   |        | 4.1.9 freertos-plus-tcp                              |

This documentation contains information specific to the imx943evk board.

# **Chapter 1**

# IMX943EVK

# Note:

IMX943EVK includes IMX943-19X19-LPDDR5-EVK, IMX943-19X19-LPDDR4-EVK, IMX943-15X15-LPDDR4-EVK

IMX943 19x19 LPDDR5 EVK(IMX943LP5EVK-19) = IMX943LP5CPU-19 SOM + X-IMX943BB IMX943 19x19 LPDDR4 EVK(IMX943LP4EVK-19) = IMX943LP4CPU-19 SOM + X-IMX943BB IMX943 15x15 LPDDR4 EVK(IMX943LP4EVK-15) = IMX943LP4CPU-15 SOM + X-IMX943BB

# 1.1 Overview

MCU device and part on board is shown below:

- Device: MIMX94398

- PartNumber: MIMX94398AVKM, MIMX94398AVMM

- Note: IMX943LP5CPU-19 SOM and IMX943LP4CPU-19 SOM boards are using the Part-Number MIMX94398AVKM - IMX943LP4CPU-15 SOM board is using the PartNumber MIMX94398AVMM

# **1.2 Getting Started with MCUXpresso SDK Package**

# 1.2.1 Getting Started with Package

#### **Overview**

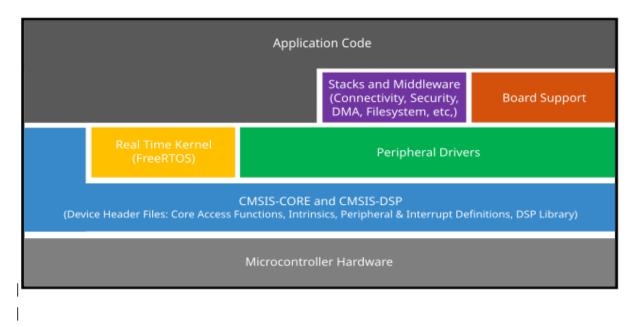

The NXP MCUXpresso software and tools offer comprehensive development solutions designed to optimize, ease and help accelerate embedded system development of applications based on general purpose, crossover and Bluetooth-enabled MCUs from NXP. The MCUXpresso SDK includes a flexible set of peripheral drivers designed to speed up and simplify development of embedded applications. Along with the peripheral drivers, the MCUXpresso SDK provides an extensive and rich set of example applications covering everything from basic peripheral use case examples to demo applications. The MCUXpresso SDK also contains optional RTOS integrations such as FreeRTOS and Azure RTOS, and device stack to support rapid development on devices.

For supported toolchain versions, see *MCUXpresso SDK Release Notes for IMX943-EVK (document MCUXSDKIMX943EVKRN)*.

For the latest version of this and other MCUXpresso SDK documents, see the MCUXpresso SDK homepage MCUXpresso-SDK: Software Development Kit for MCUXpresso.

#### **MCUXpresso SDK board support folders**

MCUXpresso SDK board support provides example applications for NXP development and evaluation boards for Arm Cortex-M cores. Board support packages are found inside of the top level boards folder, and each supported board has its own folder (MCUXpresso SDK package can support multiple boards). Within each <board\_name> folder there are various sub-folders to classify the type of examples they contain. These include (but are not limited to):

- cmsis\_driver\_examples: Simple applications intended to concisely illustrate how to use CM-SIS drivers.

- demo\_apps: Full-featured applications intended to highlight key functionality and use cases of the target MCU. These applications typically use multiple MCU peripherals and may leverage stacks and middleware.

- driver\_examples: Simple applications intended to concisely illustrate how to use the MCUXpresso SDK's peripheral drivers for a single use case.

- rtos\_examples: Basic FreeRTOS OS examples showcasing the use of various RTOS objects (semaphores, queues, and so on) and interfacing with the MCUXpresso SDK's RTOS drivers

• multicore\_examples: Simple applications intended to concisely illustrate how to use middle-ware/multicore stack.

**Example application structure** This section describes how the various types of example applications interact with the other components in the MCUXpresso SDK. To get a comprehensive understanding of all MCUXpresso SDK components and folder structure, see *MCUXpresso SDK API Reference Manual*.

Each <code><board\_name></code> folder in the boards directory contains a comprehensive set of examples that are relevant to that specific piece of hardware. Although we use the <code>hello\_world\_sm</code> example (part of the <code>demo\_apps</code> folder), the same general rules apply to any type of example in the <code><board\_name></code> folder.

In the hello\_world\_sm application folder you see the following contents:

| armgcc                                                           |

|------------------------------------------------------------------|

| iar iar                                                          |

| board.c Board macro definitions (LEDs, buttons, etc)             |

| board.h                                                          |

| clock_config.c Application-specific clock configuration          |

|                                                                  |

| demo_name.bin> Pre-compiled application                          |

| demo_name.c                                                      |

| demo_name.xml> Project definition file for MCUXpresso IDE and PG |

| pin_mux.c                                                        |

| pin_mux.h                                                        |

| readme.txt Description and instructions for running              |

|                                                                  |

|                                                                  |

All files in the application folder are specific to that example, so it is easy to copy and paste an existing example to start developing a custom application based on a project provided in the MCUXpresso SDK.

#### **Parent topic:***MCUXpresso SDK board support folders*

**Locating example application source files** When opening an example application in any of the supported IDEs, a variety of source files are referenced. The MCUXpresso SDK devices folder is the central component to all example applications. It means the examples reference the same source files and, if one of these files is modified, it could potentially impact the behavior of other examples.

The main areas of the MCUXpresso SDK tree used in all example applications are:

- devices/<device\_name>: The device's CMSIS header file, MCUXpresso SDK feature file and a few other files

- devices/<device\_name>/cmsis\_drivers: All the CMSIS drivers for your specific MCU

- device\_name>/drivers: All of the peripheral drivers for your specific MCU

- $\rm devices/<device\_name>/<tool\_name>:$  Toolchain-specific startup code, including vector table definitions

- $\rm devices/<device\_name>/utilities:$  Items such as the debug console that are used by many of the example applications

- $\bullet$  devices/<devices\_name>/project\_template: Project template used in CMSIS PACK new project creation

For examples containing an RTOS, there are references to the appropriate source code. RTOSes are in the rtos folder. The core files of each of these are shared, so modifying one could have potential impacts on other projects that depend on that file.

**Parent topic:***MCUXpresso SDK board support folders*

#### **Toolchain introduction**

The MCUXpresso SDK release for i.MX 943 includes the build system to be used with some toolchains. In this chapter, the toolchain support is presented and detailed.

#### Build a demo application using Arm GCC

This section describes the steps to configure the command-line Arm GCC tools to build, run, and debug demo applications. Additionally, this section lists the necessary driver libraries provided in the MCUXpresso SDK. The hello\_world\_sm demo application targeted for the IMX943 series hardware platform is used as an example, though these steps can be applied to any board, demo, or example application in the MCUXpresso SDK.

**Linux OS host** The following sections provide steps to run a demo compiled with Arm GCC on Linux host.

**Parent topic:***Build a demo application using Arm GCC*

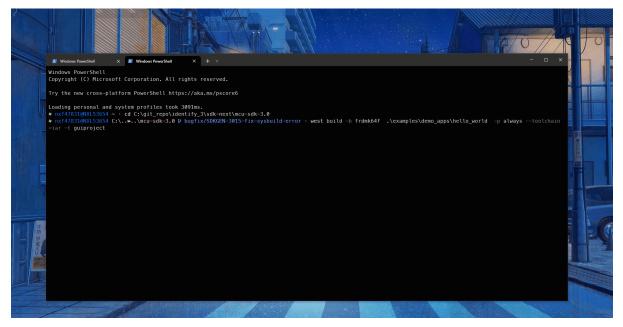

**Windows OS host** The following sections provide steps to run a demo compiled with Arm GCC on Windows OS host.

**Parent topic:***Build a demo application using Arm GCC*

#### Build a demo application with IAR

This section describes the steps to run the example applications provided in the MCUXpresso SDK. The demo application targeted for the i.MX 943 hardware platform is used as an example, although these steps can be applied to any example application in the MCUXpresso SDK.

**Build an example application** The following steps guide you through opening the hello\_world example application. These steps may change slightly for other example applications, as some of these applications may have additional layers of folders in their paths.

1. If not already done, open the desired demo application workspace. Most example application workspace files can be located using the following path:

$<\!\!install\_dir\!>\!/boards/<\!\!board\_name\!>\!/<\!\!example\_type\!>\!/<\!\!application\_name\!>\!/iar$

Using the i.MX 943 EVK board as an example, the workspace is located in:

$<\!\!install\_dir\!>\!/boards/imx943evk/demo\_apps/hello\_world/iar/hello\_world.eww$

- 2. Select the desired build target from the drop-down. For this example, select **hello\_world debug**.

- 3. To build the demo application, click **Make**.

- 4. The build completes without errors.

5. Rename the generated hello\_world.bin to m70\_image.bin/m71\_image.bin/m33s\_image.bin, then copy it to the uuu tool directory.

Parent topic:Generate flash.bin

#### Generate a flash.bin

1. Get basic images and the imx-mkimage source repository from corresponding Linux BSP release. These below basic images can to be put into imx-mkimage/iMX94:

- oei-m33-ddr.bin

- m33\_image.bin (m33\_image-mx94alt.bin: the image is generated by the command - make config=mx94alt all;m33\_image-mx94evk.bin: the image is generated by the command - make config=mx94evk all)

- m70\_image.bin (demo binary name for cortex-m7 core0 in M70 MIX)

- m71\_image.bin (demo binary name for cortex-m7 core1 in M71 MIX)

- m33s\_image.bin (demo binary name for cortex-m33 core1 in NETC MIX)

- <lpddr type name>\_dmem\_qb\_v202409.bin(lpddr type name: lpddr5 or lpddr4x)

- <lpddr type name>\_dmem\_v202409.bin

- <lpddr type name>\_imem\_qb\_v202409.bin

- <lpddr type name>\_imem\_v202409.bin

- u-boot.bin

- u-boot-spl.bin

- bl31.bin

- tee.bin

- mx943a0-ahab-container.img

#### Note:

- mx943evk for m33\_image.bin is used for rpmsg str echo, rpmsg ping pong and power\_mode\_switch\_rtos.

- mx943alt for m33\_image.bin is used for almost other examples.

- 2. Copy binary built by ARMGCC/IAR into imx-mkimage/iMX94, and rename them to m70\_image.bin/m71\_image.bin/m33s\_image.bin.

- 3. Generate flash.bin.

- make SOC=iMX94 OEI=YES flash\_all LPDDR\_TYPE=lpddr5 (Boot up Cortex-A cores and Cortex-M cores[cortex-m33 core1, cortex-m7 core0, cortex-m7 core1])

or

• make SOC=iMX94 OEI=YES flash\_m33s\_m70\_m71 LPDDR\_TYPE=lpddr5 (Boot up Cortex-M cores[cortex-m33 core1, cortex-m7 core0, cortex-m7 core1])

#### Note:

- For LPDDR5, LPDDR\_TYPE=lpddr5;For LPDDR4, LPDDR\_TYPE=lpddr4x.

- Valid combination demos to avoid resource conflict.

- Any demo on cm33\_core1, hello\_world demo on cm7 core0 and cm7 core1

- Any demo on cm7\_core0, hello\_world demo on cm33 core1 and cm7 core1

- Any demo on cm7\_core1, hello\_world demo on cm33 core1 and cm7 core0

4. Burn flash.bin to MicroSD/eMMC at 32 K(0x8000) offset with dd or HxD or UUU and then plug the MicroSD card to the board.

#### For example:

• Burn flash.bin into Micro SD card with dd

dd if=flash.bin of=/dev/sdh bs=1k seek=32 && sync

- Burn flash.bin into SD/eMMC with UUU

- 1. Connect USB Type-C port to PC through the USB cable. It is used for downloading firmware of the board.

- 2. Switch to serial downloader mode; boot core is cortex-m33. sd: uuu -b sd imx-boot-imx943-19x19-lpddr5-evk-sd.bin-flash\_all new-flash.bin

- 3. Burn flash.bin with uuu.

emmc: uuu -b emmc imx-boot-imx943-19x19-lpddr5-evk-sd.bin-flash\_all flash.bin

sd: uuu -b sd imx-boot-imx943-19x19-lpddr5-evk-sd.bin-flash\_all flash.bin

#### Note:

- imx-boot-imx943-19x19-lpddr5-evk-sd.bin-flash\_all (imx-boot-imx943-19x19-lpddr4x-evk-sd.bin-flash\_all for IMX943LP4CPU-19 SOM + X-IMX943BB;

imx-boot-imx943-15x15-lpddr4x-evk-sd.bin-flash\_all for IMX943LP4CPU-15 SOM + X-IMX943BB). Get them from linux bsp.

- flash.bin. The flash.bin is generated by yourself.

- 5. Change the boot mode to SW4[1:4] = x011 for sd boot, SW4[1:4] = x010 for emmc boot.

- 6. Power on the board .

Parent topic:Run a demo application

# Enable MCU UARTs

- 1. Connect usb typec cable from pc to typec port J15 of board.(It will emulate four serial ports[e.g. COM0 LPUART8, COM1, COM2 LPUART1, COM3 LPUART2] in pc)

- COM0(LPUART8 use as uart of cortex-m33 core1)

- COM2(LPUART1 use as uart of Cortex-A)

- COM3(LPUART2 use as uart of Cortex-m33 core0)

- 2. Connect two usb2uart converter from pc to arduino interface of board.(It will emulate two serial ports[e.g. COM4 LPUART11, COM5 LPUART12] in pc)

- COM4(LPUART11 use as uart of cortex-m7 core0)

J48-2(M2\_UART11\_RXD) – TX of usb2uart converter – pc

J48-4(M2\_UART11\_TXD) – RX of usb2uart converter – pc

GND ———— GND of usb2uart converter – pc

• COM5(LPUART12 - use as uart of cortex-m7 core1)

J44-4(M1\_UART12\_RXD) – TX of usb2uart converter – pc

J44-2(M1\_UART12\_TXD) – RX of usb2uart converter – pc

GND ———— GND of usb2uart converter – pc

Note:

- mx943evk for m33\_image.bin is used for rpmsg str echo, rpmsg ping pong and power\_mode\_switch\_rtos.

- mx943alt for m33\_image.bin is used for almost other examples.

- JTAG cannot be used when LPUART8 is used.

- Pls change uart from LPUART8 to LPUART1 and generate m33\_image.bin with command make config=mx94alt all when debugging with jtag.

- For MCUXPresso SDK

```

_boards/imx943evk/board.h

#define BOARD_DEBUG_UART_INSTANCE 8 -> #define BOARD_DEBUG_UART_

→INSTANCE 1

```

#### Parent topic:Run a demo application

#### Run a demo application

This section describes the steps to download the flash.bin to sd and emmc, run the example applications provided in the MCUXpresso SDK. The hello\_world\_sm demo application targeted for the i.MX 943 hardware platform is used as an example, although these steps can be applied to any example application in the MCUXpresso SDK.

#### Generate a flash.bin

- 1. Get basic images and the imx-mkimage source repository from corresponding Linux BSP release. These below basic images can to be put into imx-mkimage/iMX94:

- oei-m33-ddr.bin

- m33\_image.bin (m33\_image-mx94alt.bin: the image is generated by the command - make config=mx94alt all;m33\_image-mx94evk.bin: the image is generated by the command - make config=mx94evk all)

- m70\_image.bin (demo binary name for cortex-m7 core0 in M70 MIX)

- m71\_image.bin (demo binary name for cortex-m7 core1 in M71 MIX)

- m33s\_image.bin (demo binary name for cortex-m33 core1 in NETC MIX)

- <lpddr type name>\_dmem\_qb\_v202409.bin(lpddr type name: lpddr5 or lpddr4x)

- <lpddr type name>\_dmem\_v202409.bin

- <lpddr type name>\_imem\_qb\_v202409.bin

- <lpddr type name>\_imem\_v202409.bin

- u-boot.bin

- u-boot-spl.bin

- bl31.bin

- tee.bin

- mx943a0-ahab-container.img

#### Note:

- mx943evk for m33\_image.bin is used for rpmsg str echo, rpmsg ping pong and power\_mode\_switch\_rtos.

- mx943alt for  $\rm m33\_image.bin$  is used for almost other examples.

- 2. Copy binary built by ARMGCC/IAR into imx-mkimage/iMX94, and rename them to m70\_image.bin/m71\_image.bin/m33s\_image.bin.

- 3. Generate flash.bin.

- make SOC=iMX94 OEI=YES flash\_all LPDDR\_TYPE=lpddr5 (Boot up Cortex-A cores and Cortex-M cores[cortex-m33 core1, cortex-m7 core0, cortex-m7 core1])

or

• make SOC=iMX94 OEI=YES flash\_m33s\_m70\_m71 LPDDR\_TYPE=lpddr5 (Boot up Cortex-M cores[cortex-m33 core1, cortex-m7 core0, cortex-m7 core1])

#### Note:

- For LPDDR5, LPDDR\_TYPE=lpddr5;For LPDDR4, LPDDR\_TYPE=lpddr4x.

- Valid combination demos to avoid resource conflict.

- Any demo on cm33\_core1, hello\_world demo on cm7 core0 and cm7 core1

- Any demo on cm7\_core0, hello\_world demo on cm33 core1 and cm7 core1

- Any demo on cm7\_core1, hello\_world demo on cm33 core1 and cm7 core0

- 4. Burn flash.bin to MicroSD/eMMC at 32 K(0x8000) offset with dd or HxD or UUU and then plug the MicroSD card to the board.

#### For example:

- Burn flash.bin into Micro SD card with dd

- dd if=flash.bin of=/dev/sdh bs=1k seek=32 && sync

- Burn flash.bin into SD/eMMC with UUU

- 1. Connect USB Type-C port to PC through the USB cable. It is used for downloading firmware of the board.

- 2. Switch to serial downloader mode; boot core is cortex-m33. sd: uuu -b sd imx-boot-imx943-19x19-lpddr5-evk-sd.bin-flash\_all new-flash.bin

- 3. Burn flash.bin with uuu.

emmc: uuu -b emmc imx-boot-imx943-19x19-lpddr5-evk-sd.bin-flash\_all flash.bin

sd: uuu -b sd imx-boot-imx943-19x19-lpddr5-evk-sd.bin-flash\_all flash.bin

#### Note:

- imx-boot-imx943-19x19-lpddr5-evk-sd.bin-flash\_all (imx-boot-imx943-19x19-lpddr4x-evk-sd.bin-flash\_all for IMX943LP4CPU-19 SOM + X-IMX943BB;

imx-boot-imx943-15x15-lpddr4x-evk-sd.bin-flash\_all for IMX943LP4CPU-15 SOM + X-IMX943BB). Get them from linux bsp.

- flash.bin. The flash.bin is generated by yourself.

- 5. Change the boot mode to SW4[1:4] = x011 for sd boot, SW4[1:4] = x010 for emmc boot.

- 6. Power on the board .

#### Parent topic:Run a demo application

#### How to determine COM port

This section describes the steps necessary to determine the debug COM port number of your NXP hardware development platform.

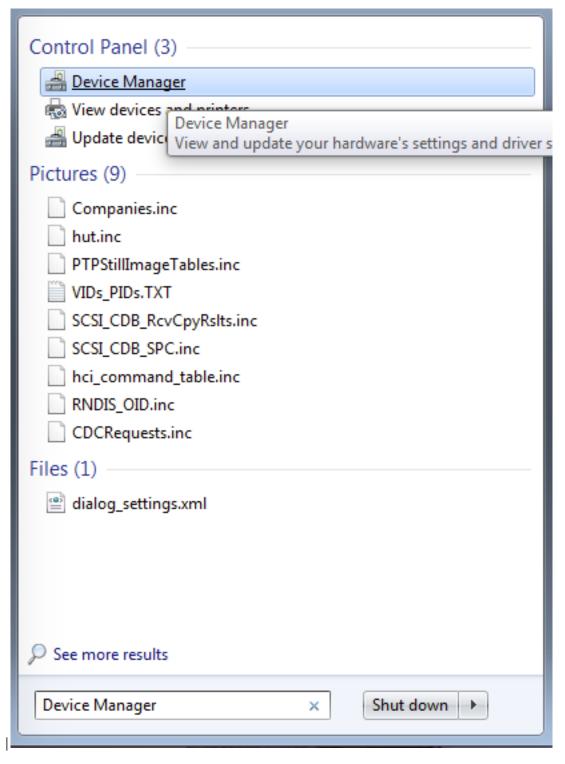

1. To determine the COM port, open the Windows operating system Device Manager. This can be achieved by going to the Windows operating system Start menu and typing **Device Manager** in the search bar, as shown in *Figure 1*.

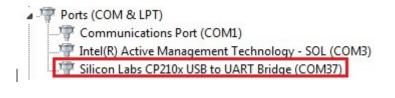

- 2. In the **Device Manager**, expand the **Ports (COM & LPT)** section to view the available ports. Depending on the NXP board you're using, the COM port can be named differently.

- 1. USB-UART interface

#### Host setup

An MCUXpresso SDK build requires that some packages are installed on the Host. Depending on the used Host operating system, the following tools should be installed.

#### Linux:

• Cmake

```

$ sudo apt-get install cmake

$ # Check the version >= 3.0.x

$ cmake --version

```

#### Windows:

• MinGW

The Minimalist GNU for Windows OS (MinGW) development tools provide a set of tools that are not dependent on third party C-Runtime DLLs (such as Cygwin). The build environment used by the SDK does not utilize the MinGW build tools, but does leverage the base install of both MinGW and MSYS. MSYS provides a basic shell with a Unix-like interface and tools.

- 1. Download the latest MinGW mingw-get-setup installer from sourceforge.net/projects/mingw/files/Installer/.

- 2. Run the installer. The recommended installation path is  $\rm CeAmGW$ , however, you may install to any location.

Note: The installation path cannot contain any spaces.

3. Ensure that mingw32-base and msys-base are selected under Basic Setup.

| Installation Package Setti | ngs   |                      |       |                   |                    |                                                 |

|----------------------------|-------|----------------------|-------|-------------------|--------------------|-------------------------------------------------|

| Basic Setup                | F F   | Package              | Class | Installed Version | Repository Version | Description                                     |

| All Packages               |       | mingw-developer-tool | bin   |                   | 2013072300         | An MSYS Installation for MinGW Developers (meta |

|                            | 🧐 r   | mingw32-base         | bin   |                   | 2013072200         | A Basic MinGW Installation                      |

|                            |       | mingw32-gcc-ada      | bin   |                   | 4.8.1-4            | The GNU Ada Compiler                            |

|                            |       | mingw32-gcc-fortran  | bin   |                   | 4.8.1-4            | The GNU FORTRAN Compiler                        |

|                            | П г   | mingw32-gcc-g++      | bin   |                   | 4.8.1-4            | The GNU C++ Compiler                            |

|                            |       | mingw32-gcc-objc     | bin   |                   | 4.8.1-4            | The GNU Objective-C Compiler                    |

|                            | (S) 1 | msys-base            | bin   |                   | 2013072300         | A Basic MSYS Installation (meta)                |

4. Click \*\*Apply Changes\*\* in the \*\*Installation\*\* menu and follow the remaining instructions to complete  $\rightarrow$  the installation.

```

|![](../images/complete\_mingw\_and\_msys\_installation.png "Complete MinGW and MSYS installation")

```

5. Add the appropriate item to the Windows operating system path environment variable. It can be found ounder \*\*Control Panel\*\*-\>\*\*System and Security\*\*-\>\*\*System\*\*-\>\*\*Advanced System Settings\*\* in othe \*\*Environment Variables...\*\* section. The path is: `<mingw\_install\_dir>\bin`.

Assuming the default installation path, `C:\MinGW`, an example is as shown in [Figure 3](host\_setup.md  $\rightarrow$ #ADDINGPATH). If the path is not set correctly, the toolchain does not work.

(continues on next page)

(continued from previous page)

\*\*Note: \*\* If you have `C:\MinGW\msys\x.x\bin` in your PATH variable \(as required by KSDK 1.0.0 \), \_  $\rightarrow$  remove it to ensure that the new GCC build system works correctly.

[![](../images/add\_path\_to\_systems\_environment.png "Add Path to systems environment")

- Cmake

- 1. Download CMake 3.0.x from www.cmake.org/cmake/resources/software.html.

- 2. Install CMake, ensuring that the option **Add CMake to system PATH** is selected when installing. The user chooses to select whether it is installed into the PATH for all users or just the current user. In this example, it is installed for all users.

| A                    |                             |                         |          |      |

|----------------------|-----------------------------|-------------------------|----------|------|

|                      | Install Opti                |                         |          |      |

|                      | Choose opt                  | ions for installing CMa | ke 3.0.2 |      |

| By default CMa       | ke does not add its directo | ory to the system PAT   | н.       |      |

|                      |                             |                         |          |      |

| Do not add           | CMake to the system PAT     |                         |          |      |

|                      | to the system PATH for al   |                         |          |      |

|                      | to the system PATH for cu   |                         |          |      |

| U national and       |                             |                         |          |      |

|                      |                             |                         |          |      |

| Create CMa           | ke Desktop Icon             |                         |          |      |

|                      |                             |                         |          |      |

|                      |                             |                         |          |      |

|                      |                             |                         |          |      |

|                      |                             |                         |          |      |

|                      |                             |                         |          |      |

| ulleaft Taskall Curr | ham 112 46                  |                         |          |      |

| ullsoft Install Sys  | tem v2.46                   |                         |          |      |

| ullsoft Install Sys  | tem v2.46                   | < Back                  | Next >   | Cano |

| ullsoft Install Sys  | tem v2.46                   | < Back                  | Next >   | Cano |

3. Follow the remaining instructions of the installer.

4. You may need to reboot your system for the PATH changes to take effect.

# 1.3 Getting Started with MCUXpresso SDK GitHub

# 1.3.1 Getting Started with MCUXpresso SDK Repository

# Installation

NOTE

If the installation instruction asks/selects whether to have the tool installation path added to the PATH variable, agree/select the choice. This option ensures that the tool can be used in any terminal in any path. *Verify the installation* after each tool installation.

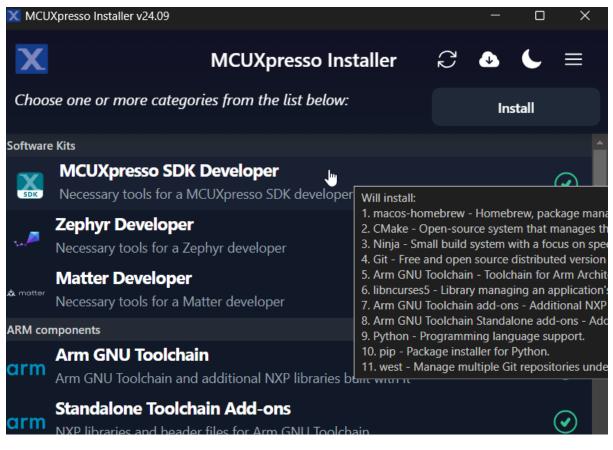

**Install Prerequisites with MCUXpresso Installer** The MCUXpresso Installer offers a quick and easy way to install the basic tools needed. The MCUXpresso Installer can be obtained from https://github.com/nxp-mcuxpresso/vscode-for-mcux/wiki/Dependency-Installation. The MCUX-presso Installer is an automated installation process, simply select MCUXpresso SDK Developer from the menu and click install. If you prefer to install the basic tools manually, refer to the next section.

# **Alternative: Manual Installation**

#### **Basic tools**

**Git** Git is a free and open source distributed version control system. Git is designed to handle everything from small to large projects with speed and efficiency. To install Git, visit the official Git website. Download the appropriate version(you may use the latest one) for your operating system (Windows, macOS, Linux). Then run the installer and follow the installation instructions.

User git --version to check the version if you have a version installed.

Then configure your username and email using the commands:

```

git config --global user.name "Your Name"

```

```

git config --global user.email "youremail@example.com"

```

#### **Python** Install python 3.10 or latest. Follow the Python Download guide.

Use python --version to check the version if you have a version installed.

#### **West** Please use the west version equal or greater than 1.2.0

# Note: you can add option '--default-timeout=1000' if you meet connection issue. Or you may set a different → source using option '-i'.

# for example, in China you could try: pip install -U west -i https://pypi.tuna.tsinghua.edu.cn/simple

pip install -U west

#### **Build And Configuration System**

**CMake** It is strongly recommended to use CMake version equal or later than 3.30.0. You can get latest CMake distributions from the official CMake download page.

For Windows, you can directly use the .msi installer like cmake-3.31.4-windows-x86\_64.msi to install.

For Linux, CMake can be installed using the system package manager or by getting binaries from the official CMake download page.

After installation, you can use cmake --version to check the version.

**Ninja** Please use the ninja version equal or later than 1.12.1.

By default, Windows comes with the Ninja program. If the default Ninja version is too old, you can directly download the ninja binary and register the ninja executor location path into your system path variable to work.

For Linux, you can use your system package manager or you can directly download the ninja binary to work.

After installation, you can use ninja --version to check the version.

**Kconfig** MCUXpresso SDK uses Kconfig python implementation. We customize it based on our needs and integrate it into our build and configuration system. The Kconfiglib sources are placed under mcuxsdk/scripts/kconfig folder.

Please make sure *python* environment is setup ready then you can use the Kconfig.

**Ruby** Our build system supports IDE project generation for iar, mdk, codewarrior and xtensa to provide OOBE from build to debug. This feature is implemented with ruby. You can follow the guide ruby environment setup to setup the ruby environment. Since we provide a built-in portable ruby, it is just a simple one cmd installation.

If you only work with CLI, you can skip this step.

**Toolchain** MCUXpresso SDK supports all mainstream toolchains for embedded development. You can install your used or interested toolchains following the guides.

| Toolchain                        | Download and Installation Guide                           | Note                |    |         |

|----------------------------------|-----------------------------------------------------------|---------------------|----|---------|

| Armgcc                           | Arm GNU Toolchain Install Guide                           | ARMGCC<br>toolchain | is | default |

| IAR                              | IAR Installation and Licensing quick ref-<br>erence guide |                     |    |         |

| MDK                              | MDK Installation                                          |                     |    |         |

| Armclang                         | Installing Arm Compiler for Embedded                      |                     |    |         |

| Zephyr                           | Zephyr SDK                                                |                     |    |         |

| Codewarrior                      | NXP CodeWarrior                                           |                     |    |         |

| Xtensa                           | Tensilica Tools                                           |                     |    |         |

| NXP S32Compiler RISC-<br>V Zen-V | NXP Website                                               |                     |    |         |

After you have installed the toolchains, register them in the system environment variables. This will allow the west build to recognize them:

| Toolchain                             | Environ-<br>ment<br>Variable | Example                                                                                                                                                        | Cmd<br>Line Ar-<br>gument          |

|---------------------------------------|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|

| Armgcc                                | AR-<br>MGCC_DIR              | C:\armgcc for windows/usr for Linux. Typically<br>arm-none-eabi-* is installed under /usr/bin                                                                  | –<br>toolchain<br>armgcc           |

| IAR                                   | IAR_DIR                      | C:\iar\ewarm-9.60.3 for Windows/opt/iarsystems/<br>bxarm-9.60.3 for Linux                                                                                      | –<br>toolchain<br>iar              |

| MDK                                   | MDK_DIR                      | $\rm C:\Keil\_v5$ for Windows.MDK IDE is not officially supported with Linux.                                                                                  | –<br>toolchain<br>mdk              |

| Armclang                              | ARM-<br>CLANG_DIF            | C:\ArmCompilerforEmbedded6.22 for Windows/opt/<br>ArmCompilerforEmbedded6.21 for Linux                                                                         | –<br>toolchain<br>mdk              |

| Zephyr                                | ZEPHYR_SE                    | c:\NXP\zephyr-sdk- <version> for windows/opt/<br/>zephyr-sdk-<version> for Linux</version></version>                                                           | –<br>toolchain<br>zephyr           |

| CodeWar-<br>rior                      | CW_DIR                       | $\label{eq:CWMCUv11.2} for windows Code Warrior is not supported with Linux$                                                                                   | –<br>toolchain<br>code-<br>warrior |

| Xtensa                                | XCC_DIR                      | C:\xtensa\XtDevTools\install\tools\RI-2023.11-win32\<br>XtensaTools for windows/opt/xtensa/XtDevTools/<br>install/tools/RI-2023.11-Linux/XtensaTools for Linux | –<br>toolchain<br>xtensa           |

|                                       |                              |                                                                                                                                                                |                                    |

| NXP<br>S32Compiler<br>RISC-V<br>Zen-V | RISCVL-<br>LVM_DIR           | C:\riscv-llvm-win32_b298_b298_2024.08.12 for Win-<br>dows/opt/riscv-llvm-Linux-x64_b298_b298_2024.08.12<br>for Linux                                           | –<br>toolchain<br>riscvl-<br>lvm   |

• The <toolchain>\_DIR is the root installation folder, not the binary location folder. For IAR, it is directory containing following installation folders:

- MDK IDE using armclang toolchain only officially supports Windows. In Linux, please directly use armclang toolchain by setting ARMCLANG\_DIR. In Windows, since most Keil users will install MDK IDE instead of standalone armclang toolchain, the MDK\_DIR has higher priority than ARMCLANG\_DIR.

- For Xtensa toolchain, please set the XTENSA\_CORE environment variable. Here's an example list:

| Device Core      | XTENSA_CORE                   |

|------------------|-------------------------------|

| RT500 fusion1    | nxp_rt500_RI23_11_newlib      |

| RT600 hifi4      | $nxp_rt600_RI23_11_newlib$    |

| RT700 hifi1      | $rt700_hifi1_RI23_11_nlib$    |

| RT700 hifi4      | $t700\_hifi4\_RI23\_11\_nlib$ |

| i.MX8ULP fusion1 | $fusion_nxp02_dsp_prod$       |

• In Windows, the short path is used in environment variables. If any toolchain is using the long path, you can open a command window from the toolchain folder and use below command to get the short path: for %i in (.) do echo %~fsi

**Tool installation check** Once installed, open a terminal or command prompt and type the associated command to verify the installation.

If you see the version number, you have successfully installed the tool. Else, check whether the tool's installation path is added into the PATH variable. You can add the installation path to the PATH with the commands below:

• Windows: Open command prompt or powershell, run below command to show the user PATH variable.

reg query HKEY\_CURRENT\_USER\Environment /v PATH

The tool installation path should be C:\Users\xxx\AppData\Local\Programs\Git\cmd. If the path is not seen in the output from above, append the path value to the PATH variable with the command below:

```

reg add HKEY_CURRENT_USER\Environment /v PATH /d "%PATH%;C:\Users\xxx\AppData\

→Local\Programs\Git\cmd"

```

Then close the command prompt or powershell and verify the tool command again.

• Linux:

- 1. Open the \$HOME/.bashrc file using a text editor, such as vim.

- 2. Go to the end of the file.

- 3. Add the line which appends the tool installation path to the PATH variable and export PATH at the end of the file. For example, export PATH="/Directory1:\$PATH".

- 4. Save and exit.

- 5. Execute the script with source .bashrc or reboot the system to make the changes live. To verify the changes, run echo \$PATH.

- macOS:

- 1. Open the \$HOME/.bash\_profile file using a text editor, such as nano.

- 2. Go to the end of the file.

- 3. Add the line which appends the tool installation path to the PATH variable and export PATH at the end of the file. For example, export PATH="/Directory1:\$PATH".

- 4. Save and exit.

- 5. Execute the script with **source** .bash\_profile **or reboot** the system to make the changes live. To verify the changes, run echo \$PATH.

#### Get MCUXpresso SDK Repo

**Establish SDK Workspace** To get the MCUXpresso SDK repository, use the west tool to clone the manifest repository and checkout all the west projects.

| # Initialize west with the manifest repository                                   |

|----------------------------------------------------------------------------------|

| west init -m https://github.com/nxp-mcuxpresso/mcuxsdk-manifests/ mcuxpresso-sdk |

|                                                                                  |

| # Update the west projects                                                       |

| cd mcuxpresso-sdk                                                                |

| west update                                                                      |

|                                                                                  |

| # Allow the usage of west extensions provided by MCUXpresso SDK                  |

| west config commands.allow_extensions true                                       |

**Install Python Dependency(If do tool installation manually)** To create a Python virtual environment in the west workspace core repo directory mcuxsdk, follow these steps:

1. Navigate to the core directory:

#### cd mcuxsdk

2. [Optional] Create and activate the virtual environment: If you don't want to use the python virtual environment, skip this step. We strongly suggest you use venv to avoid conflicts with other projects using python.

python -m venv .venv

# For Linux/MacOS

source .venv/bin/activate

# For Windows

.\.venv\Scripts\activate

# If you are using powershell and see the issue that the activate script cannot be run.

# You may fix the issue by opening the powershell as administrator and run below command:

powershell Set-ExecutionPolicy RemoteSigned

# then run above activate command again.

Once activated, your shell will be prefixed with (.venv). The virtual environment can be deactivated at any time by running deactivate command.

**Remember to activate the virtual environment every time you start working in this directory.** If you are using some modern shell like zsh, there are some powerful plugins to help you auto switch venv among workspaces. For example, zsh-autoswitch-virtualenv.

3. Install the required Python packages:

# Note: you can add option '--default-timeout=1000' if you meet connection issue. Or you may set a∟ → different source using option '-i'. # for example, in China you could try: pip3 install -r mcuxsdk/scripts/requirements.txt -i https://pypi. → tuna.tsinghua.edu.cn/simple pip install -r scripts/requirements.txt

# **Explore Contents**

This section helps you build basic understanding of current fundamental project content and guides you how to build and run the provided example project in whole SDK delivery.

**Folder View** The whole MCUXpresso SDK project, after you have done the west init and west update operations follow the guideline at *Getting Started Guide*, have below folder structure:

| Folder         | Description                                                                            |

|----------------|----------------------------------------------------------------------------------------|

| mani-<br>fests | Manifest repo, contains the manifest file to initialize and update the west workspace. |

| mcuxsdk        | The MCUXpresso SDK source code, examples, middleware integration and script files.     |

All the projects record in the Manifest repo are checked out to the folder mcuxsdk/, the layout of mcuxsdk folder is shown as below:

| Folder               | Description                                                                                                                                                                                   |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| arch                 | Arch related files such as ARM CMSIS core files, RISC-V files and the build files related to the architecture.                                                                                |

| cmake                | The cmake modules, files which organize the build system.                                                                                                                                     |

| com-<br>po-<br>nents | Software components.                                                                                                                                                                          |

| de-<br>vices         | Device support package which categorized by device series. For each device, header file, feature file, startup file and linker files are provided, also device specific drivers are included. |

| docs                 | Documentation source and build configuration for this sphinx built online documen-<br>tation.                                                                                                 |

| drivers              | Peripheral drivers.                                                                                                                                                                           |

| ex-<br>am-<br>ples   | Various demos and examples, support files on different supported boards. For each board support, there are board configuration files.                                                         |

| mid-<br>dle-<br>ware | Middleware components integrated into SDK.                                                                                                                                                    |

| rtos                 | Rtos components integrated into SDK.                                                                                                                                                          |

| scripts              | Script files for the west extension command and build system support.                                                                                                                         |

| svd                  | Svd files for devices, this is optional because of large size. Customers run west manifest config group.filter +optional and west update mcux-soc-svd to get this folder.                     |

**Examples Project** The examples project is part of the whole SDK delivery, and locates in the folder mcuxsdk/examples of west workspace.

Examples files are placed in folder of  $<\!\!{\rm example\_category}\!>$ , these examples include (but are not limited to)

- demo\_apps: Basic demo set to start using SDK, including hello\_world and led\_blinky.

- driver\_examples: Simple applications that show how to use the peripheral drivers for a single use case. These applications typically only use a single peripheral but there are cases where multiple peripherals are used (for example, SPI transfer using DMA).

Board porting layers are placed in folder of  $\_boards/<board\_name>$  which aims at providing the board specific parts for examples code mentioned above.

#### Run a demo using MCUXpresso for VS Code

This section explains how to configure MCUXpresso for VS Code to build, run, and debug example applications. This guide uses the hello\_world demo application as an example. However, these steps can be applied to any example application in the MCUXpresso SDK.

**Build an example application** This section assumes that the user has already obtained the SDK as outlined in *Get MCUXpresso SDK Repo*.

To build an example application:

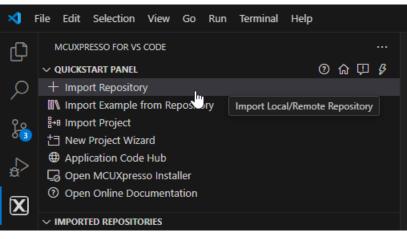

1. Import the SDK into your workspace. Click **Import Repository** from the **QUICKSTART PANEL**.

**Note:** You can import the SDK in several ways. Refer to MCUXpresso for VS Code Wiki for details.

Select **Local** if you've already obtained the SDK as seen in *Get MCUXpresso SDK Repo*. Select your location and click **Import**.

| E Import Repositor | ух               |   |               |  |        |

|--------------------|------------------|---|---------------|--|--------|

| Impor              | t Repositor      | у |               |  |        |

| REMOTE             | REMOTE ARCHIVE   |   | LOCAL ARCHIVE |  |        |

| Location:          | c:\Repos\mcuxsdk |   |               |  | Browse |

| Import             |                  |   |               |  |        |

2. Click Import Example from Repository from the QUICKSTART PANEL.

In the dropdown menu, select the MCUXpresso SDK, the Arm GNU Toolchain, your board, template, and application type. Click **Import**.

| ■ Import Example free              | om Repository X                                                                                                                                                                                                                         |             |

|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| Import                             | Example from Repository                                                                                                                                                                                                                 |             |

| Repository:                        | c:\Repos\mcuxsdk (MCUXpresso SDK Repository)                                                                                                                                                                                            | ~           |

| Toolchain:                         | (Arm GNU Toolchain 13.2.rel1 (Build arm-13.7)) 13.2.1 20231009 💿 (C:\NXP\MCUXpressol                                                                                                                                                    | DE_24.'   🗸 |

| Board:                             | FRDM-MCXC444                                                                                                                                                                                                                            | ~           |

|                                    | FRDM-MCXC444                                                                                                                                                                                                                            |             |

| Template:                          | demo_apps/hello_world                                                                                                                                                                                                                   | ~           |

| input. The purp<br>further develop | d demo prints the "Hello World" string to the terminal using the SDK UART drivers and repeat<br>lose of this demo is to show how to use the UART, and to provide a simple project for debugg<br>oment.<br>README file for more details. |             |

| App type:                          | Freestanding application                                                                                                                                                                                                                | ~           |

| Name:                              | frdmmcxc444_hello_world                                                                                                                                                                                                                 |             |

| Location:                          | c:\nxp_examples<br>Note: Path doesn't exist. Folder(s) will be created.                                                                                                                                                                 | Browse      |

| Open read                          | Ime file after project is imported                                                                                                                                                                                                      |             |

| Import                             |                                                                                                                                                                                                                                         |             |

**Note:** The MCUXpresso SDK projects can be imported as **Repository applications** or **Free-standing applications**. The difference between the two is the import location. Projects imported as Repository examples will be located inside the MCUXpresso SDK, whereas Free-standing examples can be imported to a user-defined location. Select between these by designating your selection in the **App type** dropdown menu.

- 3. VS Code will prompt you to confirm if the imported files are trusted. Click Yes.

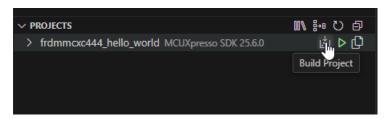

- 4. Navigate to the **PROJECTS** view. Find your project and click the **Build Project** icon.

The integrated terminal will open at the bottom and will display the build output.

| PROBLEMS OUTPUT                                              | TERMINAL PORTS                         | DEBUG CONSO                        | E SERIAL MONITOR                         | OFFLINE PERIPHERALS                                                                                                                                                                                                  | ∑ CMake: build                        |

|--------------------------------------------------------------|----------------------------------------|------------------------------------|------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|

| [18/21] Building C<br>[19/21] Building C                     | object CMakeFiles<br>object CMakeFiles | 5/hello_world.d<br>5/hello_world.d | ir/C_/Repos/mcuxso<br>ir/C_/Repos/mcuxso | dk/mcuxsdk/components/debug_console_lite/fsl_debug_console.c.obj<br>dk/mcuxsdk/devices/MCX/MCXC/MAC4/drivers/fsl_clock.c.obj<br>dk/mcuxsdk/drivers/lpuart/fsl_lpuart.c.obj<br>dk/mcuxsdk/drivers/uart/fsl_uart.c.obj |                                       |

| [21/21] Linking C @                                          |                                        |                                    |                                          |                                                                                                                                                                                                                      | i i i i i i i i i i i i i i i i i i i |

| Memory region                                                | Used Size Re                           | gion Size %age                     | Used                                     |                                                                                                                                                                                                                      | 1                                     |

| <pre>m_interrupts:</pre>                                     | 192 B                                  | 512 B 3                            | 7.50%                                    |                                                                                                                                                                                                                      |                                       |

| <pre>m_flash_config:</pre>                                   | 16 B                                   | 16 B 10                            | .00%                                     |                                                                                                                                                                                                                      |                                       |

| m text:                                                      | 7892 B                                 | 261104 B                           | 3.02%                                    |                                                                                                                                                                                                                      |                                       |

| m data:                                                      | 2128 B                                 | 32 KB                              | 5.49%                                    |                                                                                                                                                                                                                      |                                       |

| build finished successfully.                                 |                                        |                                    |                                          |                                                                                                                                                                                                                      |                                       |

| Terminal will be reused by tasks, press any key to close it. |                                        |                                    |                                          |                                                                                                                                                                                                                      |                                       |

**Run an example application** Note: for full details on MCUXpresso for VS Code debug probe support, see MCUXpresso for VS Code Wiki.

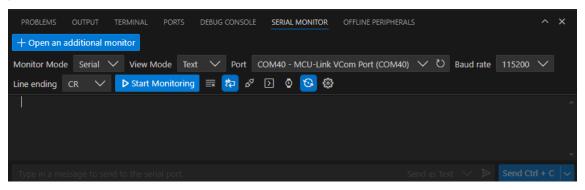

1. Open the **Serial Monitor** from the VS Code's integrated terminal. Select the VCom Port for your device and set the baud rate to 115200.

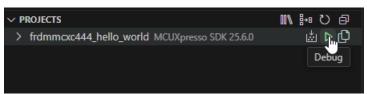

2. Navigate to the **PROJECTS** view and click the play button to initiate a debug session.

The debug session will begin. The debug controls are initially at the top.

| C hello_ | world.c ×                                                                               |

|----------|-----------------------------------------------------------------------------------------|

| frdmmcx  | c444_hello_world > examples > demo_apps > hello_world > C hello_v 🗄 IÞ 🗘 🕇 🕇 🖱 🔲   i→ 🕤 |

| 18       |                                                                                         |

| 21       |                                                                                         |

| 22       |                                                                                         |

| 23       | * Variables                                                                             |

| 24       |                                                                                         |

| 25       |                                                                                         |

| 26       |                                                                                         |

| 27       | * Code                                                                                  |

| 28       |                                                                                         |

| 29       |                                                                                         |

| 30       | * @brief Main function                                                                  |

| 31       |                                                                                         |

| 32       | int main(void)                                                                          |

| 33       | {                                                                                       |

| 34       | char ch;                                                                                |

| 35       |                                                                                         |

| 36       | /* Init board hardware. */                                                              |

| D 37     | BOARD_InitHardware();                                                                   |

| 38       |                                                                                         |

| 39       | <pre>PRINTF("hello world.\r\n");</pre>                                                  |

| 40       |                                                                                         |

| 41<br>42 | while (1)                                                                               |

| 42       |                                                                                         |

| 43<br>44 | ch = GETCHAR();<br>PUTCHAR(ch);                                                         |

| 44<br>45 |                                                                                         |

| 45<br>46 | 1                                                                                       |

| 40       |                                                                                         |

3. Click **Continue** on the debug controls to resume execution of the code. Observe the output on the **Serial Monitor**.

| PROBLEMS              | OUTPUT       | TERMINAL   | PERIPHER | ALS RTC          | DS DET | AILS PORTS | DEBUG CONSOLE    | SERIAL MONIT |

|-----------------------|--------------|------------|----------|------------------|--------|------------|------------------|--------------|

| + Open an a           | additional n | nonitor    |          |                  |        |            |                  |              |

| Monitor Mod           | e Serial `   | 🗸 View M   | ode Text |                  | Port   | COM40 - MC | U-Link VCom Port | (COM40) 🗸 i  |

| Stop Mor              | nitoring     | ېي 🔁       | D 0      | <mark>ම</mark> 🕄 |        |            |                  |              |

| Oper<br>hello wor<br> |              | erial port | COM40 -  |                  |        |            |                  |              |

#### Running a demo using ARMGCC CLI/IAR/MDK

**Supported Boards** Use the west extension west list\_project to understand the board support scope for a specified example. All supported build command will be listed in output:

west list\_project -p examples/demo\_apps/hello\_world [-t armgcc]

INFO: [1][west build -p always examples/demo\_apps/hello\_world --toolchain armgcc --config release -b\_  $\rightarrow$  evk9mimx8ulp -Dcore\_id=cm33]

INFO: [2][west build -p always examples/demo\_apps/hello\_world --toolchain armgcc --config release -b\_  $\rightarrow$  evkbimxrt1050]

$INFO: [ 3] [west build -p always examples/demo_apps/hello_world --toolchain armgcc --config release -b_{\Box} ] [west build -p always examples/demo_apps/hello_world --toolchain armgcc --config release -b_{\Box} ] [west build -p always examples/demo_apps/hello_world --toolchain armgcc --config release -b_{\Box} ] [west build -p always examples/demo_apps/hello_world --toolchain armgcc --config release -b_{\Box} ] [west build -p always examples/demo_apps/hello_world --toolchain armgcc --config release -b_{\Box} ] [west build -p always examples/demo_apps/hello_world --toolchain armgcc --config release -b_{\Box} ] [west build -p always examples/demo_apps/hello_world --toolchain armgcc --config release -b_{\Box} ] [west build -p always examples/demo_apps/hello_world --toolchain armgcc --config release -b_{\Box} ] [west build -p always examples/demo_apps/hello_world --toolchain armgcc --config release -b_{\Box} ] [west build -p always examples/demo_apps/hello_world --toolchain armgcc --config release -b_{\Box} ] [west build -p always examples/demo_apps/hello_world --toolchain armgcc --config release -b_{\Box} ] [west build -p always examples/demo_apps/hello_world --toolchain armgcc --config release -b_{\Box} ] [west build -p always examples/demo_apps/hello_world --toolchain armgcc --config release -b_{\Box} ] [west build -p always examples/hello_world --toolchain armgcc --config release -b_{\Box} ] [west build -p always examples/hello_world --toolchain armgcc --config release -b_{\Box} ] [west build -p always examples/hello_world --toolchain armgcc --config release -b_{\Box} ] [west build -p always examples/hello_world --toolchain armgcc --config release -b_{\Box} ] [west build -p always examples/hello_world --toolchain armgcc --config release -b_{\Box} ] [west build -p always examples/hello_world --toolchain armgcc --config release -b_{\Box} ] [west build --toolchain armgcc --config release -b_{\Box} ] [we$

<sup>(</sup>continues on next page)

(continued from previous page)

→evkbmimxrt1060] INFO: [ 4][west build -p always examples/demo\_apps/hello\_world --toolchain armgcc --config release -b\_ →evkbmimxrt1170 -Dcore\_id=cm4] INFO: [ 5][west build -p always examples/demo\_apps/hello\_world --toolchain armgcc --config release -b\_ →evkbmimxrt1170 -Dcore\_id=cm7] INFO: [ 6][west build -p always examples/demo\_apps/hello\_world --toolchain armgcc --config release -b\_ →evkcmimxrt1060] INFO: [ 7][west build -p always examples/demo\_apps/hello\_world --toolchain armgcc --config release -b\_ →evkcmimxrt1060] INFO: [ 7][west build -p always examples/demo\_apps/hello\_world --toolchain armgcc --config release -b\_ →evkcmimxrt1060] INFO: [ 7][west build -p always examples/demo\_apps/hello\_world --toolchain armgcc --config release -b\_ →evkcmimxr1060] INFO: [ 7][west build -p always examples/demo\_apps/hello\_world --toolchain armgcc --config release -b\_ →evkcmimxr1060]

The supported toolchains and build targets for an example are decided by the example-self example.yml and board example.yml, please refer Example Toolchains and Targets for more details.

**Build the project** Use west build -h to see help information for west build command. Compared to zephyr's west build, MCUXpresso SDK's west build command provides following additional options for mcux examples:

- --toolchain: specify the toolchain for this build, default armgcc.

- --config: value for CMAKE\_BUILD\_TYPE. If not provided, build system will get all the example supported build targets and use the first debug target as the default one. Please refer Example Toolchains and Targets for more details about example supported build targets.

Here are some typical usages for generating a SDK example:

# Generate example with default settings, default used device is the mainset MK22F51212 west build -b frdmk22f examples/demo\_apps/hello\_world

# Just print cmake commands, do not execute it west build -b frdmk22f examples/demo\_apps/hello\_world --dry-run

# Generate example with other toolchain like iar, default armgcc west build -b frdmk22f examples/demo\_apps/hello\_world --toolchain iar

# Generate example with other config type

west build -b frdmk22f examples/demo\_apps/hello\_world --config release

# Generate example with other devices with --device west build -b frdmk22f examples/demo\_apps/hello\_world --device MK22F12810 --config release

For multicore devices, you shall specify the corresponding core id by passing the command line argument -Dcore\_id. For example

west build -b evkbmimxrt 1170 examples/demo\_apps/hello\_world --toolchain iar -Dcore\_id=cm7 --config \_  $\hookrightarrow flexspi_nor_debug$

#### For shield, please use the --shield to specify the shield to run, like

west build -b mimxrt700evk --shield a 8974 examples/issdk\_examples/sensors/fxls8974cf/fxls8974cf\_poll -  $\rightarrow Dcore\_id=cm33\_core0$

**Sysbuild(System build)** To support multicore project building, we ported Sysbuild from Zephyr. It supports combine multiple projects for compilation. You can build all projects by adding --sysbuild for main application. For example:

west build -b evkbmimxrt 1170 --sysbuild ./examples/multicore\_examples/hello\_world/primary -D core\_  $\rightarrow$  id=cm7 --config flexspi\_nor\_debug --toolchain=armgcc -p always

For more details, please refer to System build.

**Config a Project** Example in MCUXpresso SDK is configured and tested with pre-defined configuration. You can follow steps blow to change the configuration.

#### 1. Run cmake configuration

west build -b evkbmimxrt1170 examples/demo\_apps/hello\_world -Dcore\_id=cm7 --cmake-only -p

Please note the project will be built without -- cmake-only parameter.

2. Run guiconfig target

west build -t guiconfig

Then you will get the Kconfig GUI launched, like

| 🔀 Hello World                                        | -       | × |

|------------------------------------------------------|---------|---|

| Save Save as Save minimal (advanced) Open            | Jump to |   |

| Show name Show all Single-menu mode                  |         |   |

| (Top)                                                |         |   |

| 🗄 Board Boot Header                                  |         | ~ |

| Project Segments                                     |         |   |

| Device Boot Header                                   |         |   |

| Device MIMXRT1176 Part (Device part MIMXRT1176DVMAA) |         |   |

| Device part MIMXRT1176DVMAA                          |         |   |

| ODevice part MIMXRT1176AVM8A                         |         |   |

| ODevice part MIMXRT1176CVM8A                         |         |   |

| Device specific drivers                              |         |   |

| XUse driver clock                                    |         |   |

| XUse driver iomuxc                                   |         |   |

| Use driver mipi csi2rx                               |         |   |

| Use driver mipi dsi                                  |         |   |

| Suse driver anatop_ai                                |         |   |

| Use driver memory                                    |         |   |

| XUse driver dcdc                                     |         |   |

| Subse driver acac                                    |         |   |

| Security gpc                                         |         |   |

| Subse driver pgric                                   |         |   |

| XUse driver src                                      |         |   |

| est any clare                                        |         | • |

Kconfig definition, with parent deps. propagated to 'depends on'

At D:/sdk\_next/mcuxsdk\devices\../devices/RT/RT1170/MIMXRT1176\drivers/Kconfig:5 Included via D:/sdk\_next/mcuxsdk/examples/demo\_apps/hello\_world/Kconfig:6 -> D:/sdk\_next/mcuxsdk/Kconfig.mcuxpresso:9 -> D:/sdk\_next/mcuxsdk\devices/Kconfig:1 -> D:/sdk\_next/mcuxsdk\devices\../devices/RT/RT1170/MIMXRT1176/Kconfig:8 Menu path: (Top)

menu "Device specific drivers"

You can reconfigure the project by selecting/deselecting Kconfig options.

After saving and closing the Kconfig GUI, you can directly run west build to build with the new configuration.

Flash Note: Please refer Flash and Debug The Example to enable west flash/debug support.

Flash the hello\_world example:

west flash -r linkserver

**Debug** Start a gdb interface by following command:

west debug -r linkserver

**Work with IDE Project** The above build functionalities are all with CLI. If you want to use the toolchain IDE to work to enjoy the better user experience especially for debugging or you are already used to develop with IDEs like IAR, MDK, Xtensa and CodeWarrior in the embedded world, you can play with our IDE project generation functionality.

This is the cmd to generate the evkbmimxrt1170 hello\_world IAR IDE project files.

west build -b evkbmimxrt1170 examples/demo\_apps/hello\_world --toolchain iar -Dcore\_id=cm7 --config\_  $\rightarrow$  flexspi\_nor\_debug -p always -t guiproject

By default, the IDE project files are generated in mcuxsdk/build/<toolchain> folder, you can open the project file with the IDE tool to work:

Note, please follow the *Installation* to setup the environment especially make sure that *ruby* has been installed.

# **1.4 Release Notes**

# 1.4.1 MCUXpresso SDK Release Notes

# **Overview**

The MCUXpresso SDK is a comprehensive software enablement package designed to simplify and accelerate application development with Arm Cortex-M-based devices from NXP, including its general purpose, crossover and Bluetooth-enabled MCUs. MCUXpresso SW and Tools for DSC further extends the SDK support to current 32-bit Digital Signal Controllers. The MCUXpresso SDK includes production-grade software with integrated RTOS (optional), integrated enabling software technologies (stacks and middleware), reference software, and more.

In addition to working seamlessly with the MCUXpresso IDE, the MCUXpresso SDK also supports and provides example projects for various toolchains. The Development tools chapter in the associated Release Notes provides details about toolchain support for your board. Support for the MCUXpresso Config Tools allows easy cloning of existing SDK examples and demos, allowing users to leverage the existing software examples provided by the SDK for their own projects.

Underscoring our commitment to high quality, the MCUXpresso SDK is MISRA compliant and checked with Coverity static analysis tools. For details on MCUXpresso SDK, see MCUXpresso-SDK: Software Development Kit for MCUXpresso.

# **MCUXpresso SDK**

As part of the MCUXpresso software and tools, MCUXpresso SDK is the evolution of Kinetis SDK, includes support for LPC, DSC, PN76, and i.MX System-on-Chip (SoC). The same drivers, APIs, and middleware are still available with support for Kinetis, LPC, DSC, and i.MX silicon. The MCUX-presso SDK adds support for the MCUXpresso IDE, an Eclipse-based toolchain that works with all MCUXpresso SDKs. Easily import your SDK into the new toolchain to access to all of the available components, examples, and demos for your target silicon. In addition to the MCUXpresso IDE, support for the MCUXpresso Config Tools allows easy cloning of existing SDK examples and demos, allowing users to leverage the existing software examples provided by the SDK for their own projects.

In order to maintain compatibility with legacy Freescale code, the filenames and source code in MCUXpresso SDK containing the legacy Freescale prefix FSL has been left as is. The FSL prefix has been redefined as the NXP Foundation Software Library.

# **Development tools**

The MCUXpresso SDK was tested with following development tools. Same versions or above are recommended.

- IAR Embedded Workbench for Arm, version is 9.60.4

- MCUXpresso for VS Code v25.06

- GCC Arm Embedded Toolchain 14.2.x

# Supported development systems

This release supports board and devices listed in following table. The board and devices in bold were tested in this release.

| Devel-<br>opment<br>boards | MCU devices                                                                                                                    |

|----------------------------|--------------------------------------------------------------------------------------------------------------------------------|

| IMX943-<br>EVK             | <b>MIMX94398AVKM</b> , MIMX94398AVMM, MIMX94398CVKM, MIMX94398CVMM, MIMX94398DVKM, MIMX94398DVMM, MIMX94398XVKM, MIMX94398XVMM |

#### MCUXpresso SDK release package

The MCUXpresso SDK release package content is aligned with the silicon subfamily it supports. This includes the boards, CMSIS, devices, middleware, and RTOS support.

**Device support** The device folder contains the whole software enablement available for the specific System-on-Chip (SoC) subfamily. This folder includes clock-specific implementation, device register header files, device register feature header files, and the system configuration source files. Included with the standard SoC support are folders containing peripheral drivers, toolchain support, and a standard debug console. The device-specific header files provide a direct access to the microcontroller peripheral registers. The device header file provides an overall SoC memory mapped register definition. The folder also includes the feature header file for each peripheral on the microcontroller. The toolchain folder contains the startup code and linker files for each supported toolchain. The startup code efficiently transfers the code execution to the main() function.

**Board support** The boards folder provides the board-specific demo applications, driver examples, and middleware examples.

**Demo application and other examples** The demo applications demonstrate the usage of the peripheral drivers to achieve a system level solution. Each demo application contains a readme file that describes the operation of the demo and required setup steps. The driver examples demonstrate the capabilities of the peripheral drivers. Each example implements a common use case to help demonstrate the driver functionality.

#### RTOS

**FreeRTOS** Real-time operating system for microcontrollers from Amazon

#### Middleware

**CMSIS DSP Library** The MCUXpresso SDK is shipped with the standard CMSIS development pack, including the prebuilt libraries.

**USB Type-C PD Stack** See the *MCUXpresso SDK USB Type-C PD Stack User's Guide* (document MCUXSDKUSBPDUG) for more information

**USB Host, Device, OTG Stack** See the MCUXpresso SDK USB Stack User's Guide (document MCUXSDKUSBSUG) for more information.

**TinyCBOR** Concise Binary Object Representation (CBOR) Library

**PKCS#11** The PKCS#11 standard specifies an application programming interface (API), called "Cryptoki," for devices that hold cryptographic information and perform cryptographic functions. Cryptoki follows a simple object based approach, addressing the goals of technology independence (any kind of device) and resource sharing (multiple applications accessing multiple devices), presenting to applications a common, logical view of the device called a "cryptographic token".

Multicore Multicore Software Development Kit