Pixel buffer enumerations#

This section provides an overview of the pixel buffer enumerations.

vg_lite_buffer_format_t enumeration#

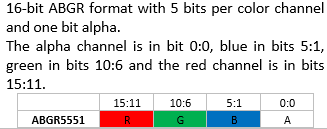

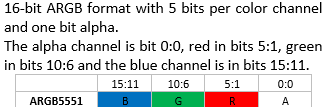

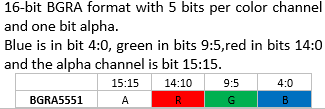

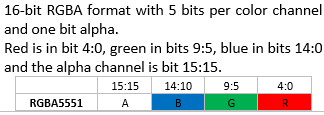

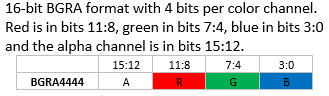

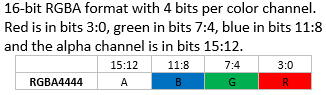

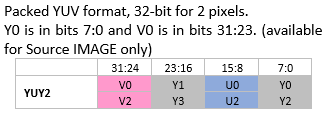

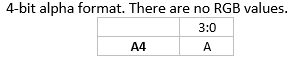

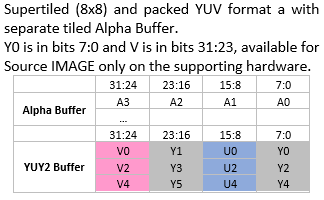

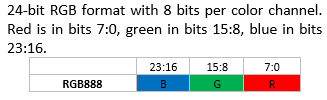

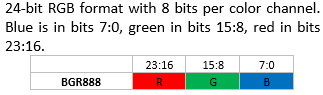

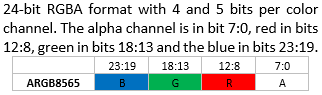

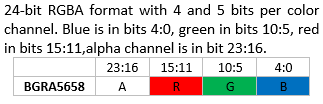

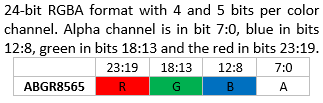

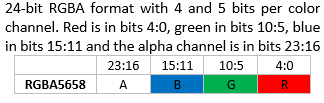

This enumeration specifies the color format to use for a buffer. This applies to both image and Render Target. Formats include supported swizzles for RGB. For YUV swizzles, use the related values and parameters in vg_lite_swizzle_t.

The application shall use the vg_lite_query_feature API to determine support for some hardware-specific formats. For example, related vg_lite_feature_t enum values include gcFEATURE_BIT_VG_RGBA2_FORMAT and gcFEATURE_BIT_VG_IM_INDEX_FORMAT.

(Alignment columns refined March and Sept 2023)

Used in structure: vg_lite_buffer_t.

See also vg_lite_blit, vg_lite_clear, vg_lite_draw.

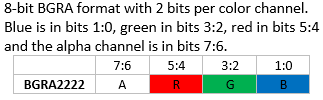

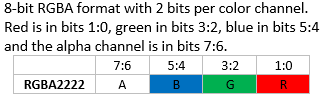

Attention: OpenVG VGImageFormat Note: The bits for each color channel are stored within a machine word from MSB to LSB in the order indicated by the pixel format name. This is the opposite of the original VG_LITE_* formats that are ordered from LSB to MSB. The formats with the same organization are listed in the same row as their VG_Lite counterparts.

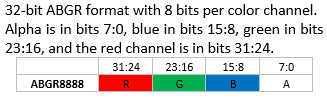

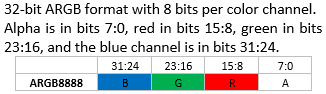

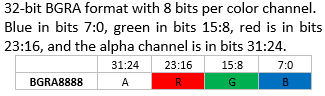

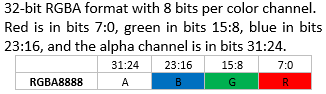

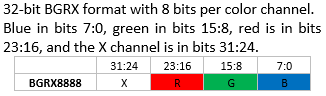

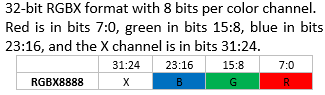

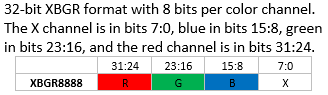

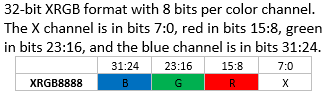

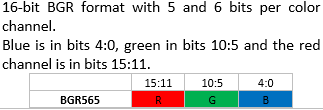

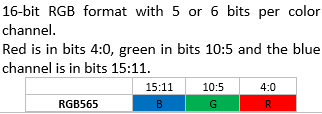

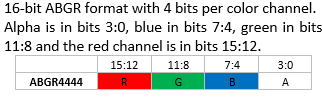

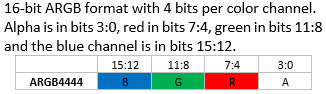

Attention: Original VGLite API Image Format Note: The bits for each color channel are stored within a machine word from LSB to MSB in the order indicated by the pixel format name. This is the opposite of the OPENVG VG_* formats that are ordered from MSB to LSB.

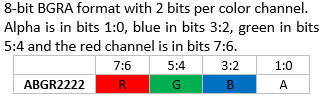

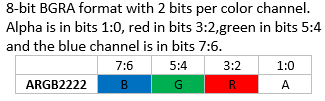

The following codes, as also used in OpenVG 1.1 Specification Table 11, are used for format description:

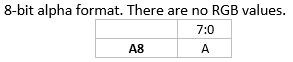

A - Alpha channel

B - Blue color channel

G - Green color channel

R - Red color channel

X - Uninterpreted padding byte or bit

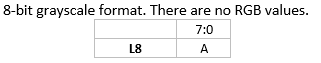

L - Grayscale

BW - 1-bit black and white

l - Linear color space

s - Non-linear (sRGB) color space

PRE - Alpha values are premultiplied

vg_lite_buffer_format_t String Value |

Description |

Supported as source |

Supported as destination |

Start address/ Stride alignment: bytes |

|---|---|---|---|---|

|

|

Yes |

Yes |

Start 4B / Stride 64B |

|

|

Yes |

Yes |

Start 4B / Stride 64B |

|

|

Yes |

Yes |

Start 4B / Stride 64B |

|

|

Yes |

Yes |

Start 4B / Stride 64B |

|

|

Yes |

Yes |

Start 4B / Stride 64B |

|

|

Yes |

Yes |

Start 4B / Stride 64B |

|

|

Yes |

Yes |

Start 4B / Stride 64B |

|

|

Yes |

Yes |

Start 4B / Stride 64B |

|

|

Yes |

Yes |

Start 4B / Stride 32B |

|

|

Yes |

Yes |

Start 4B / Stride 32B |

|

|

Yes |

Yes |

Start 4B / Stride 32B |

|

|

Yes |

Yes |

Start 4B / Stride 32B |

|

|

Yes |

Yes |

Start 4B / Stride 32B |

|

|

Yes |

Yes |

Start 4B / Stride 32B |

|

|

Yes |

Yes |

Start 4B / Stride 32B |

|

|

Yes |

Yes |

Start 4B / Stride 32B |

|

|

Yes |

Yes |

Start 4B / Stride 32B |

|

|

Yes |

Yes |

Start 4B / Stride 32B |

|

|

Yes |

No |

Start 4B / Stride 32B |

|

|

Yes |

No |

Start 4B / Stride 8B |

|

|

Yes |

Yes |

Start 4B / Stride 16B |

|

|

Yes |

Yes |

Start 4B / Stride 16B |

Hardware-dependent formats for vg_lite_buffer_format_t |

Description |

Supported as source |

Supported as destination |

Alignment (bytes) |

|---|---|---|---|---|

|

|

Yes |

Yes |

Start 4B / Stride 16B |

|

|

Yes |

Yes |

Start 4B / Stride 16B |

|

|

Yes |

Yes |

Start 4B / Stride 16B |

|

|

Yes |

No |

8B |

|

1-bit index format |

Yes |

No |

8B |

|

2-bit index format |

Yes |

No |

both 8B |

|

4-bit index format |

Yes |

No |

both 8B |

|

8-bit index format |

Yes |

No |

both 16B |

|

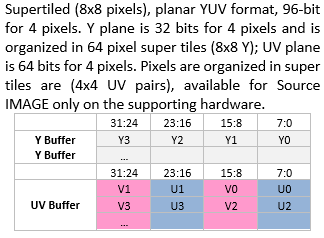

|

Yes |

No |

Y: both 16 Bytes UV: both 8 Bytes |

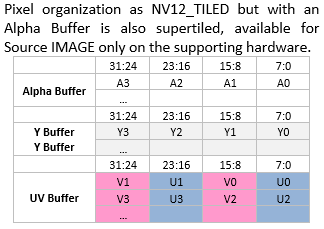

|

|

Yes |

No |

A, Y: both 16 Bytes UV: both 8 Bytes |

|

|

Yes |

No |

both 32B |

|

|

Yes |

Yes |

Start 4B / Stride 32B |

|

|

Yes |

Yes |

|

|

|

Yes |

Yes |

|

|

|

Yes |

Yes |

Start 4B / Stride 32B |

|

|

Yes |

Yes |

Start 4B / Stride 32B |

|

|

Yes |

Yes |

Start 4B / Stride 32B |

Parent topic:Pixel buffer enumerations

Image buffer alignment requirement#

The image (or source) buffer alignment requirement depends on the specific pixel format, and some gcFEATURE_*_ALIGNED defines in the vg_lite_options.h file.

Image format |

Bits per pixel |

Source tile mode |

Start address alignment requirement in bytes |

Stride alignment requirement in bytes |

Buffer height alignment requirement |

Supported for destination |

|---|---|---|---|---|---|---|

VG_LITE_INDEX1 |

1 |

linear |

8B |

2B |

1 |

|

VG_LITE_INDEX1 |

1 |

tile |

8B |

1B |

4 |

|

VG_LITE_INDEX2 |

2 |

linear |

8B |

4B |

1 |

|

VG_LITE_INDEX2 |

2 |

tile |

8B |

1B |

4 |

|

VG_LITE_INDEX4 |

4 |

linear |

8B |

8B |

1 |

|

VG_LITE_INDEX4 |

4 |

tile |

8B |

2B |

4 |

|

VG_LITE_INDEX8 |

8 |

linear |

16B |

16B |

1 |

|

VG_LITE_INDEX8 |

8 |

tile |

16B |

4B |

4 |

|

VG_LITE_A4 |

4 |

linear |

8B |

8B |

1 |

|

VG_LITE_A4 |

4 |

tile |

8B |

2B |

4 |

|

VG_LITE_A8 |

8 |

linear |

16B |

16B |

1 |

Yes |

VG_LITE_A8 |

8 |

tile |

16B |

4B |

4 |

Yes |

VG_LITE_L8 |

8 |

linear |

16B |

16B |

1 |

Yes |

VG_LITE_L8 |

8 |

tile |

16B |

4B |

4 |

Yes |

VG_LITE_ARGB2222 |

8 |

linear |

16B |

16B |

1 |

Yes |

VG_LITE_ARGB2222 |

8 |

tile |

16B |

4B |

4 |

Yes |

VG_LITE_RGB565 |

16 |

linear |

32B |

32B |

1 |

Yes |

VG_LITE_RGB565 |

16 |

tile |

32B |

8B |

4 |

Yes |

VG_LITE_ARGB1555 |

16 |

linear |

32B |

32B |

1 |

Yes |

VG_LITE_ARGB1555 |

16 |

tile |

32B |

8B |

4 |

Yes |

VG_LITE_ARGB4444 |

16 |

linear |

32B |

32B |

1 |

Yes |

VG_LITE_ARGB4444 |

16 |

tile |

32B |

8B |

4 |

Yes |

VG_LITE_ARGB8888 |

32 |

linear |

64B |

64B |

1 |

Yes |

VG_LITE_ARGB8888 |

32 |

tile |

64B |

16B |

4 |

Yes |

VG_LITE_XRGB8888 |

32 |

linear |

64B |

64B |

1 |

Yes |

VG_LITE_XRGB8888 |

32 |

tile |

64B |

16B |

4 |

Yes |

VG_LITE_ARGB8565 |

24 |

linear |

64B |

48B* |

1 |

Yes |

VG_LITE_ARGB8565 |

24 |

tile |

64B |

12B* |

4 |

Yes |

VG_LITE_RGB888 |

24 |

linear |

64B |

48B* |

1 |

Yes |

VG_LITE_RGB888 |

24 |

tile |

64B |

12B* |

4 |

Yes |

VG_LITE_YUY2/UYVY |

16 |

linear |

32B |

32B |

1 |

|

VG_LITE_YUY2/UYVY |

16 |

tile |

32B |

8B |

4 |

|

VG_LITE_NV12 |

12 |

linear |

Y: 32B UV: 32B |

Y: 32B UV: 32B |

1 |

|

VG_LITE_YV12 |

12 |

linear |

Y: 32B U: 16B V: 16B |

Y: 32B U: 16B V: 16B |

1 |

|

VG_LITE_NV16 |

16 |

linear |

Y: 32B UV: 32B |

Y: 32B UV: 32B |

1 |

|

VG_LITE_YV16 |

16 |

linear |

Y: 32B U: 16B V: 16B |

Y: 32B U: 16B V: 16B |

1 |

|

VG_LITE_YV24 |

24 |

linear |

Y: 32B U: 32B V: 32B |

Y: 32B U: 32B V: 32B |

1 |

|

VG_LITE_ETC2 |

8 |

tile |

16B |

4B |

4 |

Note:

The values in the table reflect the alignment requirements of the data in memory. The stride of ARGB8888 / ARGB8565 is seen as 4Byte per pixel when configuring the hardware.

For tile mode, the stride is still the byte size of a row of pixels in the buffer instead of 4 rows.

When DECNano function is enabled for the buffer, the total buffer size need align to 64Byte*compression rate for ARGB8888 or XRGB8888 format, align to 48Byte*compress rate for RGB888 format.

Additional Alignment Requirement

Buffer starting address must be 16 pixel-byte-size aligned, that is 8 bit-per-pixel format buffer must be 16 bytes aligned; 16 bit-per-pixel format buffer must be 32 bytes aligned; 24 and 32 bit-per-pixel format buffer must be 64 bytes aligned.

For linear mode buffer, the buffer stride must be 16 pixel-byte-size aligned.

For tile mode buffer, buffer width and height must be 4 pixel aligned so buffer width and height end at tile boundary.

Parent topic:Pixel buffer enumerations

Destination buffer alignment requirement#

The destination (or render target) buffer alignment requirement depends on the specific pixel format, and some gcFEATURE_*_ALIGNED defines in the vg_lite_options.h file.

Target format |

Bits per pixel |

Target tile mode |

VG tile mode |

Start address alignment requirement in bytes |

Stride alignment requirement in bytes |

Buffer height alignment requirement |

|---|---|---|---|---|---|---|

VG_LITE_A8 |

8 |

linear |

linear |

4B |

1B |

1 |

VG_LITE_A8 |

8 |

linear |

tile |

64B |

64B |

4 |

VG_LITE_A8 |

8 |

tile |

linear |

64B |

64B |

4 |

VG_LITE_A8 |

8 |

tile |

tile |

64B |

16B |

4 |

VG_LITE_L8 |

8 |

linear |

linear |

4B |

1B |

1 |

VG_LITE_L8 |

8 |

linear |

tile |

64B |

64B |

4 |

VG_LITE_L8 |

8 |

tile |

linear |

64B |

64B |

4 |

VG_LITE_L8 |

8 |

tile |

tile |

64B |

16B |

4 |

VG_LITE_ARGB2222 |

8 |

linear |

linear |

4B |

1B |

1 |

VG_LITE_ARGB2222 |

8 |

linear |

tile |

64B |

64B |

4 |

VG_LITE_ARGB2222 |

8 |

tile |

linear |

64B |

64B |

4 |

VG_LITE_ARGB2222 |

8 |

tile |

tile |

64B |

16B |

4 |

VG_LITE_RGB565 |

16 |

linear |

linear |

4B |

2B |

1 |

VG_LITE_RGB565 |

16 |

linear |

tile |

64B |

64B |

4 |

VG_LITE_RGB565 |

16 |

tile |

linear |

64B |

64B |

4 |

VG_LITE_RGB565 |

16 |

tile |

tile |

64B |

16B |

4 |

VG_LITE_ARGB1555 |

16 |

linear |

linear |

4B |

2B |

1 |

VG_LITE_ARGB1555 |

16 |

linear |

tile |

64B |

64B |

4 |

VG_LITE_ARGB1555 |

16 |

tile |

linear |

64B |

64B |

4 |

VG_LITE_ARGB1555 |

16 |

tile |

tile |

64B |

16B |

4 |

VG_LITE_ARGB4444 |

16 |

linear |

linear |

4B |

2B |

1 |

VG_LITE_ARGB4444 |

16 |

linear |

tile |

64B |

64B |

4 |

VG_LITE_ARGB4444 |

16 |

tile |

linear |

64B |

64B |

4 |

VG_LITE_ARGB4444 |

16 |

tile |

tile |

64B |

16B |

4 |

VG_LITE_ARGB8888 |

32 |

linear |

linear |

4B |

4B |

1 |

VG_LITE_ARGB8888 |

32 |

linear |

tile |

64B |

64B |

4 |

VG_LITE_ARGB8888 |

32 |

tile |

linear |

64B |

64B |

4 |

VG_LITE_ARGB8888 |

32 |

tile |

tile |

64B |

16B |

4 |

VG_LITE_XRGB8888 |

32 |

linear |

linear |

4B |

4B |

1 |

VG_LITE_XRGB8888 |

32 |

linear |

tile |

64B |

64B |

4 |

VG_LITE_XRGB8888 |

32 |

tile |

linear |

64B |

64B |

4 |

VG_LITE_XRGB8888 |

32 |

tile |

tile |

64B |

16B |

4 |

VG_LITE_ARGB8565 |

24 |

linear |

linear |

64B |

3B* |

1 |

VG_LITE_ARGB8565 |

24 |

linear |

tile |

64B |

48B* |

4 |

VG_LITE_ARGB8565 |

24 |

tile |

linear |

64B |

48B* |

4 |

VG_LITE_ARGB8565 |

24 |

tile |

tile |

64B |

12B* |

4 |

VG_LITE_RGB888 |

24 |

linear |

linear |

64B |

3B* |

1 |

VG_LITE_RGB888 |

24 |

linear |

tile |

64B |

48B* |

4 |

VG_LITE_RGB888 |

24 |

tile |

linear |

64B |

48B* |

4 |

VG_LITE_RGB888 |

24 |

tile |

tile |

64B |

12B* |

4 |

Note:

The values in the table reflect the alignment requirements of pixel data in memory. The stride of ARGB8888/ARGB8565 is seen as 4 Bytes per pixel when configuring the hardware.

For tile mode, the buffer stride is still the byte size of a row of pixels instead of 4 rows of pixels.

For PE clear function, the clear size must align to 48 Bytes for the RGB888 or ARGB8565 format.

For PE clear function with DECNano enabled, the clear size must align to 48 Bytes for RGB888, align to 64 Bytes for ARGB8888 or XRGB8888.

If the DECNano function is enabled for the buffer, the target buffer start address needs to align to 64 Bytes.

If the DECNano function is enabled for the buffer, the total buffer size needs to align to a 64-byte compression rate for ARGB8888 or XRGB8888 format and align to a 48 Byte*compression rate for RGB888 format.

Additional Alignment Requirement

Buffer starting address must be at least 4-byte aligned. Buffer stride must be at least one pixel size aligned.

Buffer starting address must be 64-byte aligned for 24 bit-per-pixel format, or tile mode, or DECNano enabled.

Buffer height must be 4-pixel aligned for tile mode buffer.

For tile mode buffer, the buffer stride must be 16-byte aligned for non-24bit-per-pixel formats. So, 8 bits-per-pixel format buffer width must be 16-pixel aligned; 16 bits-per-pixel format buffer width must be 8-pixel aligned; 32 bit-per-pixel format buffer width must be 4 pixel aligned.

For tile mode buffer, the buffer stride must be 12-byte aligned for 24 bits-per-pixel formats, that is, the buffer width must be 4-pixel aligned.

For PE clear function, the clear size must align to 48 Bytes for 24-bits-per-pixel formats.

For PE clear function with DECNano enabled, the clear size must align to 48 Bytes for 24 bits-per-pixel formats and align to 64 Bytes for 32 bits-per-pixel formats.

If source buffer tile mode is different from destination buffer tile mode, buffer starting address must be 64 Byte aligned, buffer stride must be 64 Byte aligned for non-24 bits-per-pixel formats, buffer stride must be 48-Byte aligned for 24 bits-per-pixel formats.

VGLite hardware requires the raster image width to be a multiple of 16 pixels for linear gradient and radial gradient operations. This requirement applies to all image formats. Therefore, the user must pad an arbitrary image width to a multiple of 16 pixels for VGLite linear gradient and radial gradient APIs.

Parent topic:Pixel buffer enumerations

vg_lite_buffer_layout_t enumeration#

Specifies the buffer data layout in memory.

Used in structure: vg_lite_buffer.

vg_lite_buffer_layout_t String Value |

Description |

|---|---|

|

Linear (scanline) layout. |

|

Data is organized in 4x4 pixel tiles. Note: for this layout, the buffer start address and stride must be 64-byte aligned |

Parent topic:Pixel buffer enumerations

vg_lite_compress_mode_t enumeration#

Specifies the DECNano comprssion mode. (from March 2023)

Used in structure: vg_lite_buffer_t.

vg_lite_compress_mode_t string value |

Description |

|---|---|

|

Disable compression. |

|

compression ratio is 1.6 for ARGB8888, 2.0 for XRGB8888 |

|

compression ratio is 2.0 for ARGB8888, 2.6 for XRGB8888 |

|

compression ratio is 2.6 for ARGB8888, 4.0 for XRGB8888 |

Parent topic:Pixel buffer enumerations

vg_lite_gamma_conversion_t enumeration#

Specifies the gamma conversion mode (from Sept 2022)

Used in function: vg_lite_set_gamma.

vg_lite_gamma_conversion_t string value |

Description |

|---|---|

|

Leave the color as it is. |

|

Convert from sRGB to linear. |

|

Convert from linear to sRGB space. |

Parent topic:Pixel buffer enumerations

vg_lite_index_endian_t enumeration#

Specifies the endian order parsing mode for index formats (from March 2023).

Used in structure: vg_lite_buffer_t.

vg_lite_index_endian_t string value |

Description |

|---|---|

|

Parse the index pixel from low to high, when using index1, the parsing order is bit0~bit7. when using index2, the parsing order is bit0:1,bit2:3,bit4:5.bit6:7. when using index4, the parsing order is bit0:3,bit4:7. |

|

Parse the index pixel from low to high, when using index1, the parsing order is bit7~bit0. when using index2, the parsing order is bit7:6,bit5:4,bit3:2.bit1:0. when using index4, the parsing order is bit4:7,bit0:3. |

Parent topic:Pixel buffer enumerations

vg_lite_image_mode_t enumeration#

Specifies how an image is rendered onto a buffer (prior to Sept 2022 name was vg_lite_buffer_image_mode_t).

Used in structure: vg_lite_buffer_t.

vg_lite_image_mode_t string value |

Description |

|---|---|

|

|

|

Image drawn with blending mode |

|

Image is multiplied with paint color |

|

|

|

Image input is ignored. |

|

Parent topic:Pixel buffer enumerations

vg_lite_map_flag_t enumeration#

Specifies whether mapping is for user memory or the DMA buffer (from March 2023).

Used in function: vg_lite_map.

vg_lite_map_flag_t string value |

Description |

|---|---|

|

Mapping is for user memory. |

|

Mapping is for the DMA buffer. |

Parent topic:Pixel buffer enumerations

vg_lite_paint_type_t enumeration#

Specifies paint type (from May 2023).

Used in structure: vg_lite_buffer_t.

vg_lite_paint_type_t string value |

Description |

|---|---|

|

|

|

Color |

|

Linear Gradient |

|

Radial Gradient |

|

Pattern |

Parent topic:Pixel buffer enumerations

vg_lite_transparency_t enumeration#

Specifies the transparency mode for a buffer (prior to Sept 2022 name was vg_lite_buffer_transparency_mode_t).

Used in structure:vg_lite_buffer.

vg_lite_transparency_t string value |

Description |

|---|---|

|

Opaque image: all image pixels are copied to the VG PE for rasterization |

|

Transparent image: only the non-transparent image pixels are copied to the VG PE. Note: This mode is only valid when |

Parent topic:Pixel buffer enumerations

vg_lite_swizzle_t enumeration#

This enumeration specifies the swizzle for the UV components of YUV data.

Used in structure: vg_lite_yuvinfo.

vg_lite_swizzle_t string value |

Description |

|---|---|

|

U in lower bits, V in upper bits |

|

V in lower bits, U in upper bits |

Parent topic:Pixel buffer enumerations

vg_lite_yuv2rgb_t enumeration#

This enumeration specifies the standard for conversion of YUV data to RGB data.

Used in structure: vg_lite_yuvinfo.

vg_lite_yuv2rgb_t string value |

Description |

|---|---|

|

YUV Converting with ITC.BT-601 standard |

|

YUV Converting with ITC.BT-709 standard |

Parent topic:Pixel buffer enumerations

Parent topic:Pixel buffers