|

MCUXpresso SDK API Reference Manual

Rev. 1

NXP Semiconductors

|

|

MCUXpresso SDK API Reference Manual

Rev. 1

NXP Semiconductors

|

The SDK provides a peripheral driver for the DPU.

The DPU module consists of many processing units, such as FetchDecode, LayerBlend, and so on. The SDK DPU driver provides separate functions for these processing units.

For a processing unit, there are three kinds of functions:

In the DPU driver, the pipeline is also treated as a processing unit. For example, the unit kDPU_PipelineExtDst0 means the pipeline with unit ExtDst0 as its endpoint. Accordingly, there are functions to initialize the pipeline and configure the pipeline.

The DPU module provides the shadow registers. The software can write to shadow registers instead of to the active configuration. When a new configuration is completed, the software can trigger the shadowed configuration to be the active configuration.

The DPU driver uses this feature. The shadow load function is enabled during the unit initialization. After all configurations in a pipeline are finished, the function DPU_TriggerPipelineShadowLoad can be called to activate the shadowed configurations. After this, the upper layer should monitor the interrupt status to make sure the shadow load is finished before a new configuration.

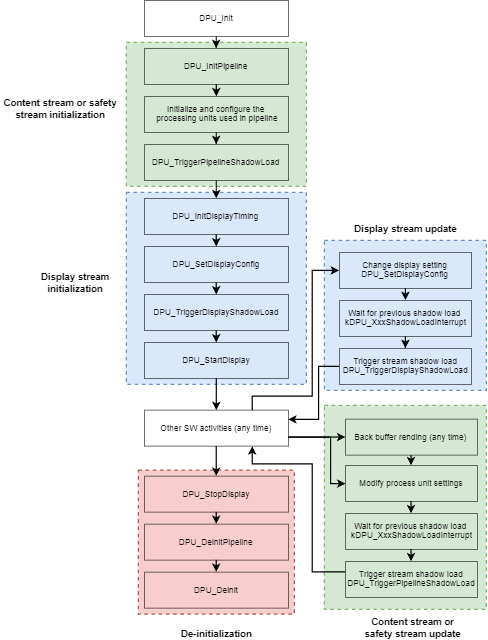

The program workflow is like this:

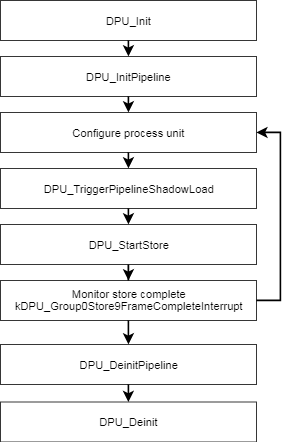

Method 1: Configure and start operation when a previous process finishes. The software workflow is:

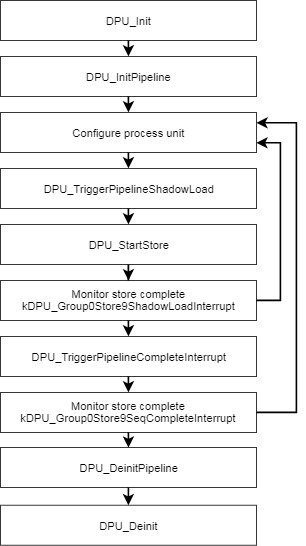

The workflow flow is:

The workflow flow is:

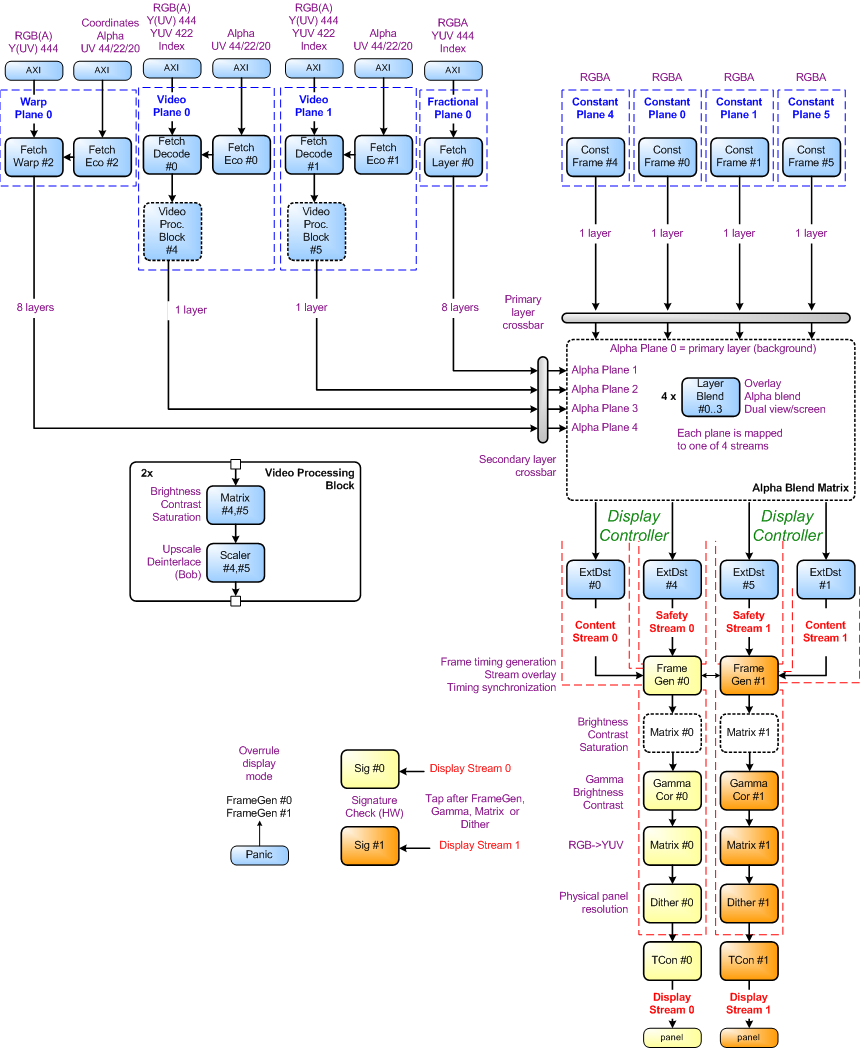

The DPU consists of many processing units. The pipeline path should configured carefully for special use cases.

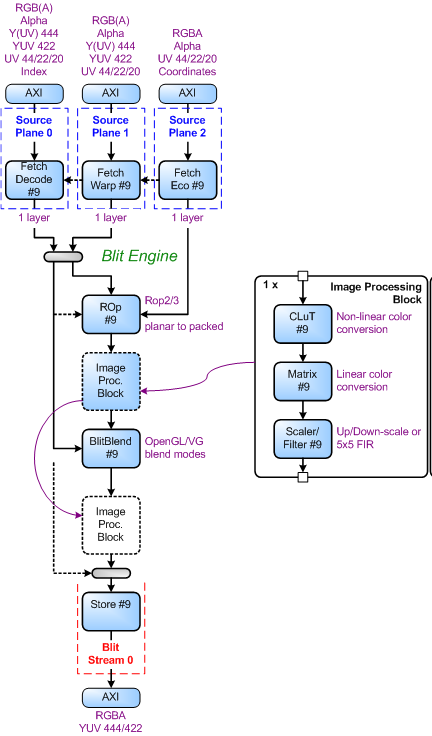

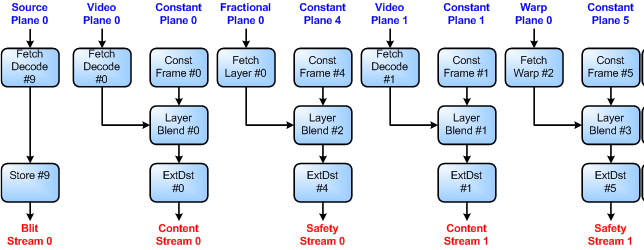

The blit engine diagram is:

The default path configuration after reset is:

Data Structures | |

| struct | dpu_fetch_unit_config_t |

| Configuration structure for fetch units. More... | |

| struct | dpu_coordinates_config_t |

| Configuration structure for the arbitrary warping re-sampling coordinates. More... | |

| struct | dpu_warp_config_t |

| Warp configuration structure for FetchWarp unit. More... | |

| struct | dpu_src_buffer_config_t |

| Fetch unit source buffer configuration structure. More... | |

| struct | dpu_clip_window_config_t |

| Fetch unit clip window configuration structure. More... | |

| struct | dpu_dst_buffer_config_t |

| Store unit Destination buffer configuration structure. More... | |

| struct | dpu_layer_blend_config_t |

| LayerBlend unit configuration structure. More... | |

| struct | dpu_blit_blend_config_t |

| BlitBlend unit configuration structure. More... | |

| struct | dpu_rop_config_t |

| ROp unit configuration structure. More... | |

| struct | dpu_const_frame_config_t |

| ConstFrame unit configuration structure. More... | |

| struct | dpu_display_timing_config_t |

| Display timing configuration structure. More... | |

| struct | dpu_display_config_t |

| Display mode configuration structure. More... | |

| struct | dpu_scaler_config_t |

| VScaler and HScaler configuration structure. More... | |

| struct | dpu_signature_config_t |

| Signature unit static configuration. More... | |

| struct | dpu_signature_window_config_t |

| Signature unit evaluation window configuration. More... | |

Macros | |

| #define | DPU_PALETTE_ENTRY_NUM (256) |

| DPU palette entery number. More... | |

| #define | DPU_MAKE_CONST_COLOR(red, green, blue, alpha) ((((uint32_t)(red)) << 24U) | (((uint32_t)(green)) << 16U) | (((uint32_t)(blue)) << 8U) | ((uint32_t)(alpha))) |

| Define the const value that write to <unit>_ConstantColor. More... | |

Driver version | |

| #define | FSL_DPU_DRIVER_VERSION (MAKE_VERSION(2, 0, 0)) |

| DPU driver version 2.0.0. More... | |

Macros for the DPU unit input source. | |

The DPU unit input source is controlled by the register pixencfg_<unit>_dynamic, the macros DPU_MAKE_SRC_REG1, DPU_MAKE_SRC_REG2, and DPU_MAKE_SRC_REG3 are used to define the register value of pixencfg_<unit>_dynamic. DPU_MAKE_SRC_REG1 defines register for DPU unit that has one input source. Accordingly, DPU_MAKE_SRC_REG2 and DPU_MAKE_SRC_REG3 are used to define the register for units that have two and three input source. See _dpu_unit_source for the input source details. | |

| #define | DPU_MAKE_SRC_REG1(src) (((uint32_t)(src)) & 0x3FU) |

| Macro for one input source unit. More... | |

| #define | DPU_MAKE_SRC_REG2(primSrc, secSrc) ((((uint32_t)(primSrc)) & 0x3FU) | (((((uint32_t)(secSrc)) & 0x3FU) << 0x8U))) |

| Macro for two input source unit. More... | |

| #define | DPU_MAKE_SRC_REG3(primSrc, secSrc, tertSrc) |

| Macro for three input source unit. More... | |

Macros define the FrameGen interrupt mode. | |

These macros are used by the function DPU_SetFrameGenInterruptConfig to set the FrameGen interrupt mode. | |

| #define | DPU_FRAME_GEN_INT_DISABLE 0U |

| Disable FrameGen interrupt. More... | |

| #define | DPU_FRAME_GEN_INT_PER_LINE(colNum) ((1U << 31U) | (1U << 15U) | (((uint32_t)colNum) & (0x3FFFU))) |

Generate FrameGen interrupt every line at the colnum colNum. More... | |

| #define | DPU_FRAME_GEN_INT_PER_FRAME(rowNum) ((1U << 31U) | (((uint32_t)rowNum) & 0x3FFF0000U)) |

Generate FrameGen interrupt every frame at the row rowNum. More... | |

DPU Initialization and de-initialization | |

| void | DPU_Init (IRIS_MVPL_Type *base) |

| Initializes the DPU peripheral. More... | |

| void | DPU_Deinit (IRIS_MVPL_Type *base) |

| Deinitializes the DPU peripheral. More... | |

| void | DPU_PreparePathConfig (IRIS_MVPL_Type *base) |

| Prepare the unit path configuration. More... | |

DPU interrupts | |

| void | DPU_EnableInterrupts (IRIS_MVPL_Type *base, uint8_t group, uint32_t mask) |

| Enable the selected DPU interrupts. More... | |

| void | DPU_DisableInterrupts (IRIS_MVPL_Type *base, uint8_t group, uint32_t mask) |

| Disable the selected DPU interrupts. More... | |

| uint32_t | DPU_GetInterruptsPendingFlags (IRIS_MVPL_Type *base, uint8_t group) |

| Get the DPU interrupts pending status. More... | |

| void | DPU_ClearInterruptsPendingFlags (IRIS_MVPL_Type *base, uint8_t group, uint32_t mask) |

| Clear the specified DPU interrupts pending status. More... | |

| void | DPU_SetInterruptsPendingFlags (IRIS_MVPL_Type *base, uint8_t group, uint32_t mask) |

| Set the specified DPU interrupts pending status. More... | |

| void | DPU_MaskUserInterrupts (IRIS_MVPL_Type *base, uint8_t group, uint32_t mask) |

| Mask the selected DPU user interrupts. More... | |

| void | DPU_EnableUserInterrupts (IRIS_MVPL_Type *base, uint8_t group, uint32_t mask) |

| Enable the selected DPU user interrupts. More... | |

| void | DPU_DisableUserInterrupts (IRIS_MVPL_Type *base, uint8_t group, uint32_t mask) |

| Disable the selected DPU user interrupts. More... | |

| uint32_t | DPU_GetUserInterruptsPendingFlags (IRIS_MVPL_Type *base, uint8_t group) |

| Get the DPU user interrupts pending status. More... | |

| void | DPU_ClearUserInterruptsPendingFlags (IRIS_MVPL_Type *base, uint8_t group, uint32_t mask) |

| Clear the specified DPU user interrupts pending status. More... | |

| void | DPU_SetUserInterruptsPendingFlags (IRIS_MVPL_Type *base, uint8_t group, uint32_t mask) |

| Set the specified DPU user interrupts pending status. More... | |

Shadow load related. | |

| status_t | DPU_EnableShadowLoad (IRIS_MVPL_Type *base, dpu_unit_t unit, bool enable) |

| Enable or disable the register shadowing for the DPU process units. More... | |

Pipline. | |

| void | DPU_InitPipeline (IRIS_MVPL_Type *base, dpu_unit_t unit) |

| Initialize the pipeline. More... | |

| void | DPU_DeinitPipeline (IRIS_MVPL_Type *base, dpu_unit_t unit) |

| Deinitializes the pipeline. More... | |

| void | DPU_TriggerPipelineShadowLoad (IRIS_MVPL_Type *base, dpu_unit_t unit) |

| Trigger the pipeline shadow load. More... | |

| void | DPU_TriggerPipelineCompleteInterrupt (IRIS_MVPL_Type *base, dpu_unit_t unit) |

| Trigger the pipeline. More... | |

| void | DPU_SetUnitSrc (IRIS_MVPL_Type *base, dpu_unit_t unit, uint32_t srcReg) |

| Set the DPU unit input source selection. More... | |

Fetch Units | |

The Fetch unit input frame buffer is used like this: <----------------- frameWidth -------------------->

^ +-------------------------------------------------+

| | ^ ^ Frame |

| | | | |

| | | offsetY | Clip window offsetY|

| | v | |

| |<------->+------------------|------+----+ |

frameHeight | | offsetX | Source Buffer | | | |

| | | v | | |

| | | +----------------------+ |

| | | |Clip Window | |

| | Clip window offsetX | | |

| |<-------------------->| | |

| | | | | |

| | | +----------------------+ |

| | | | | |

| | +-------------------------+----+ |

| | |

| | |

v +-------------------------------------------------+

| |

| void | DPU_FetchUnitGetDefaultConfig (dpu_fetch_unit_config_t *config) |

| Get the default configuration for fetch unit. More... | |

| void | DPU_InitFetchUnit (IRIS_MVPL_Type *base, dpu_unit_t unit, const dpu_fetch_unit_config_t *config) |

| Initialize the fetch unit. More... | |

| status_t | DPU_SetColorPaletteIndexWidth (IRIS_MVPL_Type *base, dpu_unit_t unit, uint8_t indexWidth) |

| Set the color palette index width for fetch unit. More... | |

| status_t | DPU_UpdateColorPalette (IRIS_MVPL_Type *base, dpu_unit_t unit, uint32_t startIndex, const uint32_t *palette, uint32_t count) |

| Updates the color palette for fetch unit. More... | |

| void | DPU_EnableColorPalette (IRIS_MVPL_Type *base, dpu_unit_t unit, uint8_t sublayer, bool enable) |

| Enable or disable color palette for some sublayer. More... | |

| void | DPU_CorrdinatesGetDefaultConfig (dpu_coordinates_config_t *config) |

| Get the default configuration structure for arbitrary warping re-sampling coordinates. More... | |

| status_t | DPU_InitWarpCoordinates (IRIS_MVPL_Type *base, dpu_unit_t unit, const dpu_coordinates_config_t *config) |

| Initialize the arbitrary warping coordinates. More... | |

| void | DPU_FetcUnitGetDefaultWarpConfig (dpu_warp_config_t *config) |

| Get the default warp configuration for FetchWarp unit. More... | |

| status_t | DPU_InitFetchUnitWarp (IRIS_MVPL_Type *base, dpu_unit_t unit, const dpu_warp_config_t *config) |

| Initialize the Warp function for FetchWarp unit. More... | |

| void | DPU_SrcBufferGetDefaultConfig (dpu_src_buffer_config_t *config) |

| Get default configuration structure for fetch unit source buffer. More... | |

| status_t | DPU_SetFetchUnitSrcBufferConfig (IRIS_MVPL_Type *base, dpu_unit_t unit, uint8_t sublayer, const dpu_src_buffer_config_t *config) |

| Set the fetch unit sublayer source buffer. More... | |

| void | DPU_SetFetchUnitSrcBufferAddr (IRIS_MVPL_Type *base, dpu_unit_t unit, uint8_t sublayer, uint32_t baseAddr) |

| Set the fetch unit sublayer source buffer base address. More... | |

| void | DPU_SetFetchUnitFrameSize (IRIS_MVPL_Type *base, dpu_unit_t unit, uint16_t height, uint16_t width) |

| Set the fetch unit frame size. More... | |

| void | DPU_SetFetchUnitOffset (IRIS_MVPL_Type *base, dpu_unit_t unit, uint8_t sublayer, uint16_t offsetX, uint16_t offsetY) |

| Set the fetch unit sublayer offset. More... | |

| void | DPU_EnableFetchUnitSrcBuffer (IRIS_MVPL_Type *base, dpu_unit_t unit, uint8_t sublayer, bool enable) |

| Enable or disable fetch unit sublayer source buffer. More... | |

| void | DPU_ClipWindowGetDefaultConfig (dpu_clip_window_config_t *config) |

| Get default configuration structure for clip window. More... | |

| void | DPU_SetFetchUnitClipWindowConfig (IRIS_MVPL_Type *base, dpu_unit_t unit, uint8_t sublayer, const dpu_clip_window_config_t *config) |

| Set the fetch unit sublayer clip window. More... | |

| void | DPU_EnableFetchUnitClipWindow (IRIS_MVPL_Type *base, dpu_unit_t unit, uint8_t sublayer, bool enable) |

| Enable or disable the fetch unit sublayer clip window. More... | |

| void | DPU_SetFetchUnitClipColor (IRIS_MVPL_Type *base, dpu_unit_t unit, dpu_clip_color_mode_t clipColorMode, uint8_t sublayer) |

| Set the fetch unit clip color mode. More... | |

ExtDst Units | |

| void | DPU_InitExtDst (IRIS_MVPL_Type *base, dpu_unit_t unit, uint32_t srcReg) |

| Initialize the ExtDst unit. More... | |

Store Units | |

The Store unit output buffer is like this: <-------------------- Stride -------------------->

<------------- bufferWidth ---------------->

^ +------------------------------------------------+

| | ^ | |

| | | Destination Buffer | |

| | | offsetY | |

| | v | |

| |<------->+===============+ | |

bufferHeight | | offsetX " " | |

| | " Input Frame " | |

| | " " | |

| | +===============+ | |

| | | |

| | | |

| | | |

v +------------------------------------------------+

| |

| void | DPU_InitStore (IRIS_MVPL_Type *base, dpu_unit_t unit, uint32_t srcReg) |

| Initialize the Store unit. More... | |

| status_t | DPU_SetStoreDstBufferConfig (IRIS_MVPL_Type *base, dpu_unit_t unit, const dpu_dst_buffer_config_t *config) |

| Set the Store unit Destination buffer configuration. More... | |

| void | DPU_DstBufferGetDefaultConfig (dpu_dst_buffer_config_t *config) |

| Get the default configuration for Store unit. More... | |

| void | DPU_SetStoreDstBufferAddr (IRIS_MVPL_Type *base, dpu_unit_t unit, uint32_t baseAddr) |

| Set the Store unit Destination buffer base address. More... | |

| void | DPU_SetStoreOffset (IRIS_MVPL_Type *base, dpu_unit_t unit, uint16_t offsetX, uint16_t offsetY) |

| Set the Store unit output offset. More... | |

| void | DPU_StartStore (IRIS_MVPL_Type *base, dpu_unit_t unit) |

| Start the Store unit. More... | |

Rop units | |

Rop unit combines up to three input frames to a single output frame, all having the same dimension. It supports:

| |

| void | DPU_InitRop (IRIS_MVPL_Type *base, dpu_unit_t unit, uint32_t srcReg) |

| Initialize the ROp unit. More... | |

| void | DPU_RopGetDefaultConfig (dpu_rop_config_t *config) |

| Get the default ROp unit configuration. More... | |

| void | DPU_SetRopConfig (IRIS_MVPL_Type *base, dpu_unit_t unit, const dpu_rop_config_t *config) |

| Set the ROp unit configuration. More... | |

| void | DPU_EnableRop (IRIS_MVPL_Type *base, dpu_unit_t unit, bool enable) |

| Enable or disable the ROp unit. More... | |

BlitBlend units | |

| void | DPU_InitBlitBlend (IRIS_MVPL_Type *base, dpu_unit_t unit, uint32_t srcReg) |

| Initialize the BlitBlend unit. More... | |

| void | DPU_BlitBlendGetDefaultConfig (dpu_blit_blend_config_t *config) |

| Get the default BlitBlend unit configuration. More... | |

| void | DPU_SetBlitBlendConfig (IRIS_MVPL_Type *base, dpu_unit_t unit, const dpu_blit_blend_config_t *config) |

| Set the BlitBlend unit configuration. More... | |

| void | DPU_EnableBlitBlend (IRIS_MVPL_Type *base, dpu_unit_t unit, bool enable) |

| Enable or disable the BlitBlend unit. More... | |

LayerBlend units | |

| void | DPU_LayerBlendGetDefaultConfig (dpu_layer_blend_config_t *config) |

| Get default configuration structure for LayerBlend. More... | |

| void | DPU_InitLayerBlend (IRIS_MVPL_Type *base, dpu_unit_t unit, uint32_t srcReg) |

| Initialize the LayerBlend. More... | |

| void | DPU_SetLayerBlendConfig (IRIS_MVPL_Type *base, dpu_unit_t unit, const dpu_layer_blend_config_t *config) |

| Set the LayerBlend unit configuration. More... | |

| void | DPU_EnableLayerBlend (IRIS_MVPL_Type *base, dpu_unit_t unit, bool enable) |

| Enable or disable the LayerBlend unit. More... | |

ConstFrame units | |

| void | DPU_InitConstFrame (IRIS_MVPL_Type *base, dpu_unit_t unit) |

| Initialize the ConstFrame unit. More... | |

| void | DPU_ConstFrameGetDefaultConfig (dpu_const_frame_config_t *config) |

| Get default configuration structure for ConstFrame unit. More... | |

| void | DPU_SetConstFrameConfig (IRIS_MVPL_Type *base, dpu_unit_t unit, const dpu_const_frame_config_t *config) |

| Set the ConstFrame unit configuration. More... | |

VScaler and HScaler units | |

| |

| void | DPU_InitScaler (IRIS_MVPL_Type *base, dpu_unit_t unit) |

| Initialize the VScaler or HScaler unit. More... | |

| void | DPU_ScalerGetDefaultConfig (dpu_scaler_config_t *config) |

| Get default configuration structure for VScaler and HScaler. More... | |

| void | DPU_SetScalerConfig (IRIS_MVPL_Type *base, dpu_unit_t unit, const dpu_scaler_config_t *config) |

| Set the VScaler or HScaler units configuration. More... | |

Display engine | |

| void | DPU_DisplayTimingGetDefaultConfig (dpu_display_timing_config_t *config) |

| Get default configuration structure for display mode. More... | |

| void | DPU_InitDisplayTiming (IRIS_MVPL_Type *base, uint8_t displayIndex, const dpu_display_timing_config_t *config) |

| Initialize the display timing. More... | |

| void | DPU_DisplayGetDefaultConfig (dpu_display_config_t *config) |

| Get default configuration structure for display frame mode. More... | |

| void | DPU_SetDisplayConfig (IRIS_MVPL_Type *base, uint8_t displayIndex, const dpu_display_config_t *config) |

| Set the display mode. More... | |

| void | DPU_StartDisplay (IRIS_MVPL_Type *base, uint8_t displayIndex) |

| Start the display. More... | |

| void | DPU_StopDisplay (IRIS_MVPL_Type *base, uint8_t displayIndex) |

| Stop the display. More... | |

| void | DPU_SetFrameGenInterruptConfig (IRIS_MVPL_Type *base, uint8_t displayIndex, uint8_t interruptIndex, uint32_t intConfig) |

| Clear the FrameGen unit status flags. More... | |

| void | DPU_TriggerDisplayShadowLoad (IRIS_MVPL_Type *base, uint8_t displayIndex) |

| Trigger the display stream shadow load token. More... | |

Signature unit | |

The Signature unit could compute the CRC value of interested region and compare to the reference value to detect incorrect display output. Up to 8 evaluation windows can be setup. Signature computation and reference check is done individually for each window. A pixel of the input frame does not contribute to more than one window. In case of overlapping windows, the window with larger index is on top. Alpha mask could be involved into the signature evaluation, thus any kind of shape could be monitored. Note that the mask is considered for checksum computation only, not for assignment of individual pixels to a certain evaluation window. So, a non-rectangular overlap between different windows is not possible. An evaluation window could be configured as skipped. This provides another method for monitoring non-rectangular windows. For example: +------------------------------------------------+ | | | | | +-------------------+ | | | Window 0 /////////| | | |///////////////////| | | |////////+-------------------------------+ | | |////////| Window 1 (Skipped) | | | |////////| | | | +--------| | | | | | | | +-------------------------------+ | | | +------------------------------------------------+ In this example, windows 1 is skipped, in this case, only the shadow part of window 0 is monitored. | |

| void | DPU_SignatureGetDefaultConfig (dpu_signature_config_t *config) |

| Get Signature unit default configuration. More... | |

| void | DPU_InitSignature (IRIS_MVPL_Type *base, uint8_t displayIndex, const dpu_signature_config_t *config) |

| Initialize the Signature unit. More... | |

| void | DPU_SignatureWindowGetDefaultConfig (dpu_signature_window_config_t *config) |

| Get Signature unit validate window default configuration. More... | |

| void | DPU_SetSignatureWindowConfig (IRIS_MVPL_Type *base, uint8_t displayIndex, uint8_t windowIndex, const dpu_signature_window_config_t *config) |

| Set the Signature unit evaluation window configuration. More... | |

| void | DPU_EnableSignatureWindowCompute (IRIS_MVPL_Type *base, uint8_t displayIndex, uint8_t windowIndex, bool enable) |

| Enable or disable the Signature unit evaluation window CRC value computation. More... | |

| void | DPU_EnableSignatureWindowCheck (IRIS_MVPL_Type *base, uint8_t displayIndex, uint8_t windowIndex, bool enable) |

| Enable or disable the Signature unit evaluation window CRC value check. More... | |

| void | DPU_GetSignatureWindowCrc (IRIS_MVPL_Type *base, uint8_t displayIndex, uint8_t windowIndex, uint32_t *redCRC, uint32_t *greenCRC, uint32_t *blueCRC) |

| Get the measured signature value of the evaluation window. More... | |

| void | DPU_SetSignatureWindowRefCrc (IRIS_MVPL_Type *base, uint8_t displayIndex, uint8_t windowIndex, uint32_t redCRC, uint32_t greenCRC, uint32_t blueCRC) |

| Set the reference signature value of the evaluation window. More... | |

| uint32_t | DPU_GetSignatureStatus (IRIS_MVPL_Type *base, uint8_t displayIndex) |

| Get the signature unit status. More... | |

| void | DPU_TriggerSignatureShadowLoad (IRIS_MVPL_Type *base, uint8_t displayIndex) |

| Trigger the Signature unit configuration shadow load. More... | |

| struct dpu_fetch_unit_config_t |

Data Fields | |

| uint32_t | srcReg |

| This value will be set to register pixengcfg_fetchX_dynamic to set the unit input source, see DPU_MAKE_SRC_REG1. More... | |

| uint16_t | frameHeight |

| Frame height. More... | |

| uint16_t | frameWidth |

| Frame width. More... | |

| uint32_t dpu_fetch_unit_config_t::srcReg |

| uint16_t dpu_fetch_unit_config_t::frameHeight |

| uint16_t dpu_fetch_unit_config_t::frameWidth |

| struct dpu_coordinates_config_t |

The coordinate layer supports:

Data Fields | |

| uint8_t | bitsPerPixel |

| Number of bits per pixel in the source buffer. More... | |

| uint16_t | strideBytes |

| Source buffer stride in bytes. More... | |

| uint32_t | baseAddr |

| Source buffer base address. More... | |

| uint16_t | frameHeight |

| Frame height. More... | |

| uint16_t | frameWidth |

| Frame width. More... | |

| uint8_t dpu_coordinates_config_t::bitsPerPixel |

Must be 1, 2, 4, 8, 16, 32.

| uint16_t dpu_coordinates_config_t::strideBytes |

| uint32_t dpu_coordinates_config_t::baseAddr |

| uint16_t dpu_coordinates_config_t::frameHeight |

| uint16_t dpu_coordinates_config_t::frameWidth |

| struct dpu_warp_config_t |

Data Fields | |

| uint32_t | srcReg |

| This value will be set to register pixengcfg_fetchX_dynamic to set the unit input source, see DPU_MAKE_SRC_REG1. More... | |

| uint16_t | frameHeight |

| Frame height. More... | |

| uint16_t | frameWidth |

| Frame width. More... | |

| uint8_t | warpBitsPerPixel |

| Pixel bits of the coordinate layer. More... | |

| bool | enableSymmetricOffset |

| Enables symmetric range for negative and positive coordinate values by adding an offset of +0.03125 internally to all coordinate input values. More... | |

| dpu_warp_coordinate_mode_t | coordMode |

| Coordinate layer mode. More... | |

| uint32_t | arbStartX |

| X of start point position. More... | |

| uint32_t | arbStartY |

| Y of start point position. More... | |

| uint8_t | arbDeltaYY |

| Y of vector between start and first sample point. More... | |

| uint8_t | arbDeltaYX |

| X of vector between start and first sample point. More... | |

| uint8_t | arbDeltaXY |

| Y of vector between first and second sample point. More... | |

| uint8_t | arbDeltaXX |

| X of vector between first and second sample point. More... | |

| uint32_t dpu_warp_config_t::srcReg |

| uint16_t dpu_warp_config_t::frameHeight |

| uint16_t dpu_warp_config_t::frameWidth |

| uint8_t dpu_warp_config_t::warpBitsPerPixel |

| bool dpu_warp_config_t::enableSymmetricOffset |

Recommended for small coordinate formats in DD_PNT mode.

| dpu_warp_coordinate_mode_t dpu_warp_config_t::coordMode |

| uint32_t dpu_warp_config_t::arbStartX |

Signed 16.5 fix-point. Used in D_PNT and DD_PNT.

| uint32_t dpu_warp_config_t::arbStartY |

Signed 16.5 fix-point. Used in D_PNT and DD_PNT.

| uint8_t dpu_warp_config_t::arbDeltaYY |

Signed 3.5 fix-point. Used in DD_PNT.

| uint8_t dpu_warp_config_t::arbDeltaYX |

Signed 3.5 fix-point. Used in DD_PNT.

| uint8_t dpu_warp_config_t::arbDeltaXY |

Signed 3.5 fix-point. Used in DD_PNT.

| uint8_t dpu_warp_config_t::arbDeltaXX |

Signed 3.5 fix-point. Used in DD_PNT.

| struct dpu_src_buffer_config_t |

Base address and stride alignment restrictions: 32 bpp: Base address and stride must be a multiple of 4 bytes. 16 bpp: Base address and stride must be a multiple of 2 bytes. others: any byte alignment allowed

Generally, the bitsPerPixel and pixelFormat specify the pixel format in frame buffer, they should match. But when the color palette is used, the bitsPerPixel specify the format in framebuffer, the pixelFormat specify the format in color palette entry.

Data Fields | |

| uint32_t | baseAddr |

| Source buffer base address, see alignment restrictions. More... | |

| uint16_t | strideBytes |

| Source buffer stride in bytes, see alignment restrictions. More... | |

| uint8_t | bitsPerPixel |

| Bits per pixel in frame buffer. More... | |

| dpu_pixel_format_t | pixelFormat |

| Pixel format. More... | |

| uint16_t | bufferHeight |

| Buffer height. More... | |

| uint16_t | bufferWidth |

| Buffer width. More... | |

| uint32_t | constColor |

| Const color shown in the region out of frame buffer, see DPU_MAKE_CONST_COLOR. More... | |

| uint32_t dpu_src_buffer_config_t::baseAddr |

| uint16_t dpu_src_buffer_config_t::strideBytes |

| uint8_t dpu_src_buffer_config_t::bitsPerPixel |

| dpu_pixel_format_t dpu_src_buffer_config_t::pixelFormat |

| uint16_t dpu_src_buffer_config_t::bufferHeight |

| uint16_t dpu_src_buffer_config_t::bufferWidth |

| uint32_t dpu_src_buffer_config_t::constColor |

| struct dpu_clip_window_config_t |

Data Fields | |

| uint16_t | windowOffsetX |

| Horizontal offset of the clip window. More... | |

| uint16_t | windowOffsetY |

| Vertical offset of the clip window. More... | |

| uint16_t | windowHeight |

| Height of the clip window. More... | |

| uint16_t | windowWidth |

| Width of the clip window. More... | |

| uint16_t dpu_clip_window_config_t::windowOffsetX |

| uint16_t dpu_clip_window_config_t::windowOffsetY |

| uint16_t dpu_clip_window_config_t::windowHeight |

| uint16_t dpu_clip_window_config_t::windowWidth |

| struct dpu_dst_buffer_config_t |

Base address and stride alignment restrictions: 32 bpp: Base address and stride must be a multiple of 4 bytes. 16 bpp: Base address and stride must be a multiple of 2 bytes. others: any byte alignment allowed

Data Fields | |

| uint32_t | baseAddr |

| Destination buffer base address, see alignment restrictions. More... | |

| uint16_t | strideBytes |

| Destination buffer stride in bytes, see alignment restrictions. More... | |

| uint8_t | bitsPerPixel |

| Bits per pixel. More... | |

| dpu_pixel_format_t | pixelFormat |

| Pixel format. More... | |

| uint16_t | bufferHeight |

| Buffer height. More... | |

| uint16_t | bufferWidth |

| Buffer width. More... | |

| uint32_t dpu_dst_buffer_config_t::baseAddr |

| uint16_t dpu_dst_buffer_config_t::strideBytes |

| uint8_t dpu_dst_buffer_config_t::bitsPerPixel |

| dpu_pixel_format_t dpu_dst_buffer_config_t::pixelFormat |

| uint16_t dpu_dst_buffer_config_t::bufferHeight |

| uint16_t dpu_dst_buffer_config_t::bufferWidth |

| struct dpu_layer_blend_config_t |

Data Fields | |

| uint8_t | constAlpha |

| The const alpha value used in blend. More... | |

| dpu_blend_mode_t | secAlphaBlendMode |

| Secondary (overlay) input alpha blending function. More... | |

| dpu_blend_mode_t | primAlphaBlendMode |

| Primary (background) input alpha blending function. More... | |

| dpu_blend_mode_t | secColorBlendMode |

| Secondary (overlay) input color blending function. More... | |

| dpu_blend_mode_t | primColorBlendMode |

| Primary (background) input color blending function. More... | |

| uint32_t | srcReg |

| This value will be set to pixengcfg_layerblendX_dynamic to set the unit input source, see DPU_MAKE_SRC_REG2. More... | |

| bool | enableAlphaMask |

| Enable AlphaMask feature. More... | |

| dpu_alpha_mask_mode_t | alphaMaskMode |

| AlphaMask mode, only valid when enableAlphaMask is true. More... | |

| uint8_t dpu_layer_blend_config_t::constAlpha |

| dpu_blend_mode_t dpu_layer_blend_config_t::secAlphaBlendMode |

| dpu_blend_mode_t dpu_layer_blend_config_t::primAlphaBlendMode |

| dpu_blend_mode_t dpu_layer_blend_config_t::secColorBlendMode |

| dpu_blend_mode_t dpu_layer_blend_config_t::primColorBlendMode |

| uint32_t dpu_layer_blend_config_t::srcReg |

| bool dpu_layer_blend_config_t::enableAlphaMask |

| dpu_alpha_mask_mode_t dpu_layer_blend_config_t::alphaMaskMode |

| struct dpu_blit_blend_config_t |

Data Fields | |

| uint8_t | neutralBorderRightPixels |

| Number of neutral right border pixels. More... | |

| uint8_t | neutralBorderLeftPixels |

| Number of neutral left border pixels. More... | |

| dpu_blit_blend_neutral_border_mode_t | neutralBorderMode |

| Neutral border mode. More... | |

| uint32_t | constColor |

| Const color used for blit blend, see DPU_MAKE_CONST_COLOR. More... | |

| dpu_blit_blend_func_t | redBlendFuncSrc |

| Red component source blend function. | |

| dpu_blit_blend_func_t | redBlendFuncDst |

| Red component destination blend function. | |

| dpu_blit_blend_func_t | greenBlendFuncSrc |

| Green component source blend function. | |

| dpu_blit_blend_func_t | greenBlendFuncDst |

| Green component destination blend function. | |

| dpu_blit_blend_func_t | blueBlendFuncSrc |

| Blue component source blend function. | |

| dpu_blit_blend_func_t | blueBlendFuncDst |

| Blue component destination blend function. | |

| dpu_blit_blend_func_t | alphaBlendFuncSrc |

| Alpha component source blend function. | |

| dpu_blit_blend_func_t | alphaBlendFuncDst |

| Alpha component destination blend function. | |

| dpu_blit_blend_mode_t | redBlendMode |

| Red component blend mode. | |

| dpu_blit_blend_mode_t | greenBlendMode |

| Green component blend mode. | |

| dpu_blit_blend_mode_t | blueBlendMode |

| Blue component blend mode. | |

| dpu_blit_blend_mode_t | alphaBlendMode |

| Alpha component blend mode. | |

| uint8_t dpu_blit_blend_config_t::neutralBorderRightPixels |

| uint8_t dpu_blit_blend_config_t::neutralBorderLeftPixels |

| dpu_blit_blend_neutral_border_mode_t dpu_blit_blend_config_t::neutralBorderMode |

| uint32_t dpu_blit_blend_config_t::constColor |

| struct dpu_rop_config_t |

Data Fields | |

| uint32_t | controlFlags |

| Control flags, see _dpu_rop_flags. More... | |

| uint8_t | alphaIndex |

| Alpha operation index. More... | |

| uint8_t | blueIndex |

| Blue operation index. More... | |

| uint8_t | greenIndex |

| Green operation index. More... | |

| uint8_t | redIndex |

| Red operation index. More... | |

| uint32_t dpu_rop_config_t::controlFlags |

| uint8_t dpu_rop_config_t::alphaIndex |

| uint8_t dpu_rop_config_t::blueIndex |

| uint8_t dpu_rop_config_t::greenIndex |

| uint8_t dpu_rop_config_t::redIndex |

| struct dpu_const_frame_config_t |

Data Fields | |

| uint16_t | frameHeight |

| Frame height. More... | |

| uint16_t | frameWidth |

| Frame width. More... | |

| uint32_t | constColor |

| See DPU_MAKE_CONST_COLOR. More... | |

| uint16_t dpu_const_frame_config_t::frameHeight |

| uint16_t dpu_const_frame_config_t::frameWidth |

| uint32_t dpu_const_frame_config_t::constColor |

| struct dpu_display_timing_config_t |

Data Fields | |

| uint16_t | flags |

| OR'ed value of _dpu_display_timing_flags. More... | |

| uint16_t | width |

| Active width. More... | |

| uint16_t | hsw |

| HSYNC pulse width. More... | |

| uint16_t | hfp |

| Horizontal front porch. More... | |

| uint16_t | hbp |

| Horizontal back porch. More... | |

| uint16_t | height |

| Active height. More... | |

| uint16_t | vsw |

| VSYNC pulse width. More... | |

| uint16_t | vfp |

| Vrtical front porch. More... | |

| uint16_t | vbp |

| Vertical back porch. More... | |

| uint16_t dpu_display_timing_config_t::flags |

| uint16_t dpu_display_timing_config_t::width |

| uint16_t dpu_display_timing_config_t::hsw |

| uint16_t dpu_display_timing_config_t::hfp |

| uint16_t dpu_display_timing_config_t::hbp |

| uint16_t dpu_display_timing_config_t::height |

| uint16_t dpu_display_timing_config_t::vsw |

| uint16_t dpu_display_timing_config_t::vfp |

| uint16_t dpu_display_timing_config_t::vbp |

| struct dpu_display_config_t |

Data Fields | |

| bool | enablePrimAlpha |

| Enable primary input alpha for screen composition. More... | |

| bool | enableSecAlpha |

| Enable secondary input alpha for screen composition. More... | |

| dpu_display_mode_t | displayMode |

| Display mode. More... | |

| bool | enablePrimAlphaInPanic |

| Enable primary input alpha for screen composition in panic mode. More... | |

| bool | enableSecAlphaInPanic |

| Enable secondary input alpha for screen composition in panic mode. More... | |

| dpu_display_mode_t | displayModeInPanic |

| Display mode in panic mode. More... | |

| uint16_t | constRed |

| Const red value, 10-bit. More... | |

| uint16_t | constGreen |

| Const green value, 10-bit. More... | |

| uint16_t | constBlue |

| Const green value, 10-bit. More... | |

| uint8_t | constAlpha |

| Const alpha value, 1-bit. More... | |

| uint16_t | primAreaStartX |

| Primary screen upper left corner, x component. More... | |

| uint16_t | primAreaStartY |

| Primary screen upper left corner, y component. More... | |

| uint16_t | secAreaStartX |

| Secondary screen upper left corner, x component. More... | |

| uint16_t | secAreaStartY |

| Secondary screen upper left corner, y component. More... | |

| bool dpu_display_config_t::enablePrimAlpha |

| bool dpu_display_config_t::enableSecAlpha |

| dpu_display_mode_t dpu_display_config_t::displayMode |

| bool dpu_display_config_t::enablePrimAlphaInPanic |

| bool dpu_display_config_t::enableSecAlphaInPanic |

| dpu_display_mode_t dpu_display_config_t::displayModeInPanic |

| uint16_t dpu_display_config_t::constRed |

| uint16_t dpu_display_config_t::constGreen |

| uint16_t dpu_display_config_t::constBlue |

| uint8_t dpu_display_config_t::constAlpha |

| uint16_t dpu_display_config_t::primAreaStartX |

14-bit , start from 1.

| uint16_t dpu_display_config_t::primAreaStartY |

14-bit, start from 1.

| uint16_t dpu_display_config_t::secAreaStartX |

14-bit, start from 1.

| uint16_t dpu_display_config_t::secAreaStartY |

14-bit, start from 1.

| struct dpu_scaler_config_t |

Data Fields | |

| uint32_t | srcReg |

| This value will be set to register pixengcfg_slacer_dynamic to set the unit input source, see DPU_MAKE_SRC_REG1. More... | |

| uint16_t | inputSize |

| For HScaler, it is frame width, for VScaler, it is frame height. More... | |

| uint16_t | outputSize |

| For HScaler, it is frame width, for VScaler, it is frame height. More... | |

| uint32_t dpu_scaler_config_t::srcReg |

When down-scaling horizontally, the path should be -> HScaler -> VScaler ->, When up-scaling horizontally, the path should be -> VScaler -> HScaler ->.

| uint16_t dpu_scaler_config_t::inputSize |

| uint16_t dpu_scaler_config_t::outputSize |

| struct dpu_signature_config_t |

Data Fields | |

| uint8_t | errorThreshold |

| Number of frames with signature violation before signature error is set for an evaluation window. More... | |

| uint8_t | errorResetThreshold |

| Number of consecutive frames without signature violation before signature error is reset for an evaluation window. More... | |

| uint8_t | panicRed |

| Constant color shown in the window when local panic happens. More... | |

| uint8_t | panicGreen |

| Constant color shown in the window when local panic happens. More... | |

| uint8_t | panicBlue |

| Constant color shown in the window when local panic happens. More... | |

| uint8_t | panicAlpha |

| Constant color shown in the window when local panic happens. More... | |

| uint8_t dpu_signature_config_t::errorThreshold |

| uint8_t dpu_signature_config_t::errorResetThreshold |

| uint8_t dpu_signature_config_t::panicRed |

| uint8_t dpu_signature_config_t::panicGreen |

| uint8_t dpu_signature_config_t::panicBlue |

| uint8_t dpu_signature_config_t::panicAlpha |

Must be 0 or 1

| struct dpu_signature_window_config_t |

Data Fields | |

| uint32_t | controlFlags |

| Control flags, OR'ed valud of _dpu_signature_window_flags. More... | |

| uint16_t | upperLeftX |

| X coordinate of the upper left corner. More... | |

| uint16_t | upperLeftY |

| Y coordinate of the upper left corner. More... | |

| uint16_t | lowerRightX |

| X coordinate of the lower right corner. More... | |

| uint16_t | lowerRightY |

| Y coordinate of the lower right corner. More... | |

| uint32_t dpu_signature_window_config_t::controlFlags |

| uint16_t dpu_signature_window_config_t::upperLeftX |

| uint16_t dpu_signature_window_config_t::upperLeftY |

| uint16_t dpu_signature_window_config_t::lowerRightX |

| uint16_t dpu_signature_window_config_t::lowerRightY |

| #define FSL_DPU_DRIVER_VERSION (MAKE_VERSION(2, 0, 0)) |

| #define DPU_PALETTE_ENTRY_NUM (256) |

| #define DPU_MAKE_SRC_REG1 | ( | src | ) | (((uint32_t)(src)) & 0x3FU) |

| #define DPU_MAKE_SRC_REG2 | ( | primSrc, | |

| secSrc | |||

| ) | ((((uint32_t)(primSrc)) & 0x3FU) | (((((uint32_t)(secSrc)) & 0x3FU) << 0x8U))) |

| #define DPU_MAKE_SRC_REG3 | ( | primSrc, | |

| secSrc, | |||

| tertSrc | |||

| ) |

| #define DPU_MAKE_CONST_COLOR | ( | red, | |

| green, | |||

| blue, | |||

| alpha | |||

| ) | ((((uint32_t)(red)) << 24U) | (((uint32_t)(green)) << 16U) | (((uint32_t)(blue)) << 8U) | ((uint32_t)(alpha))) |

| #define DPU_FRAME_GEN_INT_DISABLE 0U |

| #define DPU_FRAME_GEN_INT_PER_LINE | ( | colNum | ) | ((1U << 31U) | (1U << 15U) | (((uint32_t)colNum) & (0x3FFFU))) |

| #define DPU_FRAME_GEN_INT_PER_FRAME | ( | rowNum | ) | ((1U << 31U) | (((uint32_t)rowNum) & 0x3FFF0000U)) |

| enum dpu_unit_t |

| enum _dpu_interrupt |

| enum _dpu_unit_source |

| enum dpu_pixel_format_t |

To support more pixel format, enhance this enum and the array s_dpuColorComponentFormats.

| enum dpu_blend_mode_t |

| enum _dpu_rop_flags |

| enum dpu_display_mode_t |

| void DPU_Init | ( | IRIS_MVPL_Type * | base | ) |

This function ungates the DPU clock.

| base | DPU peripheral base address. |

| void DPU_Deinit | ( | IRIS_MVPL_Type * | base | ) |

This function gates the DPU clock.

| base | DPU peripheral base address. |

| void DPU_PreparePathConfig | ( | IRIS_MVPL_Type * | base | ) |

The DPU has a default path configuration. Before changing the configuration, this function could be used to break all the original path. This make sure one pixel engine unit is not used in multiple pipelines.

| base | DPU peripheral base address. |

| void DPU_EnableInterrupts | ( | IRIS_MVPL_Type * | base, |

| uint8_t | group, | ||

| uint32_t | mask | ||

| ) |

For example, to enable Store9 shadow load interrupt and Store9 frame complete interrupt, use like this:

| base | DPU peripheral base address. |

| group | Interrupt group index. |

| mask | The interrupts to enable, this is a logical OR of members in _dpu_interrupt. |

group should be passed in correctly. | void DPU_DisableInterrupts | ( | IRIS_MVPL_Type * | base, |

| uint8_t | group, | ||

| uint32_t | mask | ||

| ) |

For example, to disable Store9 shadow load interrupt and Store9 frame complete interrupt, use like this:

| base | DPU peripheral base address. |

| group | Interrupt group index. |

| mask | The interrupts to disable, this is a logical OR of members in _dpu_interrupt. |

group should be passed in correctly. | uint32_t DPU_GetInterruptsPendingFlags | ( | IRIS_MVPL_Type * | base, |

| uint8_t | group | ||

| ) |

The pending status are returned as mask. For example, to check the Store9 shadow load interrupt and Store9 frame complete interrupt pending status, use like this.

| base | DPU peripheral base address. |

| group | Interrupt group index. |

| void DPU_ClearInterruptsPendingFlags | ( | IRIS_MVPL_Type * | base, |

| uint8_t | group, | ||

| uint32_t | mask | ||

| ) |

For example, to disable Store9 shadow load interrupt and Store9 frame complete interrupt pending status, use like this:

| base | DPU peripheral base address. |

| group | Interrupt group index. |

| mask | The interrupt pending flags to clear, this is a logical OR of members in _dpu_interrupt. |

group should be passed in correctly. | void DPU_SetInterruptsPendingFlags | ( | IRIS_MVPL_Type * | base, |

| uint8_t | group, | ||

| uint32_t | mask | ||

| ) |

This function sets the interrupts pending flags, this is a method to trigger interrupts by software.

| base | DPU peripheral base address. |

| group | Interrupt group index. |

| mask | The interrupt pending flags to set, this is a logical OR of members in _dpu_interrupt. |

group should be passed in correctly. | void DPU_MaskUserInterrupts | ( | IRIS_MVPL_Type * | base, |

| uint8_t | group, | ||

| uint32_t | mask | ||

| ) |

The only difference between DPU user interrupt and normal interrupt is user interrupts could be masked by DPU_MaskUserInterrupts. All other APIs useage are the same.

| base | DPU peripheral base address. |

| group | Interrupt group index. |

| mask | The interrupts to mask, this is a logical OR of members in _dpu_interrupt. |

| void DPU_EnableUserInterrupts | ( | IRIS_MVPL_Type * | base, |

| uint8_t | group, | ||

| uint32_t | mask | ||

| ) |

The only difference between DPU user interrupt and normal interrupt is user interrupts could be masked by DPU_MaskUserInterrupts.

| base | DPU peripheral base address. |

| group | Interrupt group index. |

| mask | The interrupts to enable, this is a logical OR of members in _dpu_interrupt. |

| void DPU_DisableUserInterrupts | ( | IRIS_MVPL_Type * | base, |

| uint8_t | group, | ||

| uint32_t | mask | ||

| ) |

The only difference between DPU user interrupt and normal interrupt is user interrupts could be masked by DPU_MaskUserInterrupts.

| base | DPU peripheral base address. |

| group | Interrupt group index. |

| mask | The interrupts to disable, this is a logical OR of members in _dpu_interrupt. |

| uint32_t DPU_GetUserInterruptsPendingFlags | ( | IRIS_MVPL_Type * | base, |

| uint8_t | group | ||

| ) |

The only difference between DPU user interrupt and normal interrupt is user interrupts could be masked by DPU_MaskUserInterrupts.

| base | DPU peripheral base address. |

| group | Interrupt group index. |

| void DPU_ClearUserInterruptsPendingFlags | ( | IRIS_MVPL_Type * | base, |

| uint8_t | group, | ||

| uint32_t | mask | ||

| ) |

The only difference between DPU user interrupt and normal interrupt is user interrupts could be masked by DPU_MaskUserInterrupts.

| base | DPU peripheral base address. |

| group | Interrupt group index. |

| mask | The interrupt pending flags to clear, this is a logical OR of members in _dpu_interrupt. |

| void DPU_SetUserInterruptsPendingFlags | ( | IRIS_MVPL_Type * | base, |

| uint8_t | group, | ||

| uint32_t | mask | ||

| ) |

The only difference between DPU user interrupt and normal interrupt is user interrupts could be masked by DPU_MaskUserInterrupts.

| base | DPU peripheral base address. |

| group | Interrupt group index. |

| mask | The interrupt pending flags to set, this is a logical OR of members in _dpu_interrupt. |

| status_t DPU_EnableShadowLoad | ( | IRIS_MVPL_Type * | base, |

| dpu_unit_t | unit, | ||

| bool | enable | ||

| ) |

For example:

| base | DPU peripheral base address. |

| unit | The unit whose shadow load to enable or disable, see dpu_unit_t. |

| enable | True to enable, false to disable. |

| kStatus_Success | The shadow load is enabled or disabled successfully. |

| kStatus_InvalidArgument | The unit does not support shadow load. |

| void DPU_InitPipeline | ( | IRIS_MVPL_Type * | base, |

| dpu_unit_t | unit | ||

| ) |

| base | DPU peripheral base address. |

| unit | The DPU pipeline unit. |

| void DPU_DeinitPipeline | ( | IRIS_MVPL_Type * | base, |

| dpu_unit_t | unit | ||

| ) |

Power down the pipeline and disable the shadow load feature.

| base | DPU peripheral base address. |

| unit | The DPU pipeline unit. |

| void DPU_TriggerPipelineShadowLoad | ( | IRIS_MVPL_Type * | base, |

| dpu_unit_t | unit | ||

| ) |

This function triggers the pipeline reconfiguration.

| base | DPU peripheral base address. |

| unit | The DPU pipeline unit. |

| void DPU_TriggerPipelineCompleteInterrupt | ( | IRIS_MVPL_Type * | base, |

| dpu_unit_t | unit | ||

| ) |

This function triggers the pipeline sequence complete interrupt. After triggered, this interrupt occurs when the pipeline is empty and no more operations are pending. It will occur immediately, when this is the case already during activation of the trigger. Generally this is used for the blit operation, to make sure all operations finished.

| base | DPU peripheral base address. |

| unit | The DPU pipeline unit. |

| void DPU_SetUnitSrc | ( | IRIS_MVPL_Type * | base, |

| dpu_unit_t | unit, | ||

| uint32_t | srcReg | ||

| ) |

Sets the DPU unit input source, the input source is controlled by the register <unit>_dynamic in "Pixel Engin Top Level". This function writes the register <unit>_dynamic directly, please check the reference manual for the register details. This function only changes the input source control bits in register.

| base | DPU peripheral base address. |

| unit | The DPU pipeline unit. |

| srcReg | The value written to register <unit>_dynamic. Could be generated using DPU_MAKE_SRC_REG1, DPU_MAKE_SRC_REG2, and DPU_MAKE_SRC_REG3. |

| void DPU_FetchUnitGetDefaultConfig | ( | dpu_fetch_unit_config_t * | config | ) |

The default value is:

| config | Pointer to the configuration structure. |

| void DPU_InitFetchUnit | ( | IRIS_MVPL_Type * | base, |

| dpu_unit_t | unit, | ||

| const dpu_fetch_unit_config_t * | config | ||

| ) |

This function initializes the fetch unit for the basic use, for other use case such as arbitrary warping, use the functions DPU_InitFetchUnitWarp and DPU_InitWarpCoordinates.

The input source of fetch unit could be:

| base | DPU peripheral base address. |

| unit | DPU unit, see dpu_unit_t, must be fetch unit here. |

| config | Pointer to the configuration structure. |

| status_t DPU_SetColorPaletteIndexWidth | ( | IRIS_MVPL_Type * | base, |

| dpu_unit_t | unit, | ||

| uint8_t | indexWidth | ||

| ) |

The palette index width could be 1 to 8. Note the difference between palette index width and the pixel width in framebuffer.

| base | DPU peripheral base address. |

| unit | DPU unit, see dpu_unit_t, must be FetchDecode or FetchLayer here. |

| indexWidth | The palette index width. |

| kStatus_Success | Initialization success. |

| kStatus_InvalidArgument | Wrong argument. |

| status_t DPU_UpdateColorPalette | ( | IRIS_MVPL_Type * | base, |

| dpu_unit_t | unit, | ||

| uint32_t | startIndex, | ||

| const uint32_t * | palette, | ||

| uint32_t | count | ||

| ) |

This function updates the fetch unit color palette, the palette values specified by palette are loaded to fetch unit from startIndex. The load count is specified by count.

| base | DPU peripheral base address. |

| unit | DPU unit, see dpu_unit_t, must be FetchDecode or FetchLayer here. |

| startIndex | The start index of the fetch unit palette to update. |

| palette | Pointer to the palette. |

| count | Count of palette. |

| kStatus_Success | Initialization success. |

| kStatus_InvalidArgument | Wrong argument. |

| void DPU_EnableColorPalette | ( | IRIS_MVPL_Type * | base, |

| dpu_unit_t | unit, | ||

| uint8_t | sublayer, | ||

| bool | enable | ||

| ) |

| base | DPU peripheral base address. |

| unit | DPU unit, see dpu_unit_t, must be FetchDecode or FetchLayer here. |

| sublayer | Sublayer index, should be 0 to 7. |

| enable | True to enable, false to disable. |

| void DPU_CorrdinatesGetDefaultConfig | ( | dpu_coordinates_config_t * | config | ) |

The default value is:

| config | Pointer to the configuration structure. |

| status_t DPU_InitWarpCoordinates | ( | IRIS_MVPL_Type * | base, |

| dpu_unit_t | unit, | ||

| const dpu_coordinates_config_t * | config | ||

| ) |

This function initializes the FetchEco unit, so that it could be used as the arbitrary warping coordinates.

| base | DPU peripheral base address. |

| unit | DPU unit, see dpu_unit_t, must be FetchEco here. |

| config | Pointer to the configuration structure. |

| kStatus_Success | Initialization success. |

| kStatus_InvalidArgument | Wrong argument. |

| void DPU_FetcUnitGetDefaultWarpConfig | ( | dpu_warp_config_t * | config | ) |

The default value is:

| config | Pointer to the configuration structure. |

| status_t DPU_InitFetchUnitWarp | ( | IRIS_MVPL_Type * | base, |

| dpu_unit_t | unit, | ||

| const dpu_warp_config_t * | config | ||

| ) |

This function initializes the FetchWarp unit for the arbitrary warping.

The valid source of fetch warp unit could be:

| base | DPU peripheral base address. |

| unit | DPU unit, see dpu_unit_t, must be FetchWarp unit here. |

| config | Pointer to the configuration structure. |

| kStatus_Success | Initialization success. |

| kStatus_InvalidArgument | Wrong argument. |

| void DPU_SrcBufferGetDefaultConfig | ( | dpu_src_buffer_config_t * | config | ) |

The default value is:

| config | Pointer to the configuration structure. |

| status_t DPU_SetFetchUnitSrcBufferConfig | ( | IRIS_MVPL_Type * | base, |

| dpu_unit_t | unit, | ||

| uint8_t | sublayer, | ||

| const dpu_src_buffer_config_t * | config | ||

| ) |

| base | DPU peripheral base address. |

| unit | DPU unit, see dpu_unit_t, must be fetch unit here. |

| sublayer | Sublayer index, should be 0 to 7. |

| config | Pointer to the configuration structure. |

| kStatus_Success | Initialization success. |

| kStatus_InvalidArgument | Wrong argument. |

| void DPU_SetFetchUnitSrcBufferAddr | ( | IRIS_MVPL_Type * | base, |

| dpu_unit_t | unit, | ||

| uint8_t | sublayer, | ||

| uint32_t | baseAddr | ||

| ) |

| base | DPU peripheral base address. |

| unit | DPU unit, see dpu_unit_t, must be fetch unit here. |

| sublayer | Sublayer index, should be 0 to 7. |

| baseAddr | Source buffer base address. |

| void DPU_SetFetchUnitFrameSize | ( | IRIS_MVPL_Type * | base, |

| dpu_unit_t | unit, | ||

| uint16_t | height, | ||

| uint16_t | width | ||

| ) |

| base | DPU peripheral base address. |

| unit | DPU unit, see dpu_unit_t, must be fetch unit here. |

| height | Frame height. |

| width | Frame width. |

| void DPU_SetFetchUnitOffset | ( | IRIS_MVPL_Type * | base, |

| dpu_unit_t | unit, | ||

| uint8_t | sublayer, | ||

| uint16_t | offsetX, | ||

| uint16_t | offsetY | ||

| ) |

| base | DPU peripheral base address. |

| unit | DPU unit, see dpu_unit_t, must be fetch unit here. |

| sublayer | Sublayer index, should be 0 to 7. |

| offsetX | Horizontal offset. |

| offsetY | Vertical offset. |

| void DPU_EnableFetchUnitSrcBuffer | ( | IRIS_MVPL_Type * | base, |

| dpu_unit_t | unit, | ||

| uint8_t | sublayer, | ||

| bool | enable | ||

| ) |

| base | DPU peripheral base address. |

| unit | DPU unit, see dpu_unit_t, must be fetch unit here. |

| sublayer | Sublayer index, should be 0 to 7. |

| enable | True to enable, false to disable. |

| void DPU_ClipWindowGetDefaultConfig | ( | dpu_clip_window_config_t * | config | ) |

The default value is:

| config | Pointer to the configuration structure. |

| void DPU_SetFetchUnitClipWindowConfig | ( | IRIS_MVPL_Type * | base, |

| dpu_unit_t | unit, | ||

| uint8_t | sublayer, | ||

| const dpu_clip_window_config_t * | config | ||

| ) |

| base | DPU peripheral base address. |

| unit | DPU unit, see dpu_unit_t, must be fetch unit here. |

| sublayer | Sublayer index, should be 0 to 7. |

| config | Pointer to the configuration structure. |

| void DPU_EnableFetchUnitClipWindow | ( | IRIS_MVPL_Type * | base, |

| dpu_unit_t | unit, | ||

| uint8_t | sublayer, | ||

| bool | enable | ||

| ) |

| base | DPU peripheral base address. |

| unit | DPU unit, see dpu_unit_t, must be fetch unit here. |

| sublayer | Sublayer index, should be 0 to 7. |

| enable | True to enable, false to disable. |

| void DPU_SetFetchUnitClipColor | ( | IRIS_MVPL_Type * | base, |

| dpu_unit_t | unit, | ||

| dpu_clip_color_mode_t | clipColorMode, | ||

| uint8_t | sublayer | ||

| ) |

This function selects which color to take for pixels that do not lie inside the clip window of any layer.

| base | DPU peripheral base address. |

| unit | DPU unit, see dpu_unit_t, must be fetch unit here. |

| clipColorMode | Select null color or use sublayer color. |

| sublayer | Select which sublayer's color to use when clipColorMode is kDPU_ClipColorSublayer. |

| void DPU_InitExtDst | ( | IRIS_MVPL_Type * | base, |

| dpu_unit_t | unit, | ||

| uint32_t | srcReg | ||

| ) |

| base | DPU peripheral base address. |

| unit | DPU unit, see dpu_unit_t, must be ExtDst unit here. |

| srcReg | Input source selecte register value, pixencfg_extdstX_dynamic see DPU_MAKE_SRC_REG1. The valid source:

|

| void DPU_InitStore | ( | IRIS_MVPL_Type * | base, |

| dpu_unit_t | unit, | ||

| uint32_t | srcReg | ||

| ) |

The valid input source of the store unit could be:

| base | DPU peripheral base address. |

| unit | DPU unit, see dpu_unit_t, must be Store unit here. |

| srcReg | Input source selecte register value, pixencfg_extdstX_dynamic see DPU_MAKE_SRC_REG1. |

| status_t DPU_SetStoreDstBufferConfig | ( | IRIS_MVPL_Type * | base, |

| dpu_unit_t | unit, | ||

| const dpu_dst_buffer_config_t * | config | ||

| ) |

| base | DPU peripheral base address. |

| unit | DPU unit, see dpu_unit_t, must be Store unit here. |

| config | Pointer to the configuration. |

| kStatus_Success | Initialization success. |

| kStatus_InvalidArgument | Wrong argument. |

| void DPU_DstBufferGetDefaultConfig | ( | dpu_dst_buffer_config_t * | config | ) |

The default value is:

| config | Pointer to the configuration. |

| void DPU_SetStoreDstBufferAddr | ( | IRIS_MVPL_Type * | base, |

| dpu_unit_t | unit, | ||

| uint32_t | baseAddr | ||

| ) |

This function is run time used for better performance.

| base | DPU peripheral base address. |

| unit | DPU unit, see dpu_unit_t, must be Store unit here. |

| baseAddr | Base address of the Destination buffer to set. |

| void DPU_SetStoreOffset | ( | IRIS_MVPL_Type * | base, |

| dpu_unit_t | unit, | ||

| uint16_t | offsetX, | ||

| uint16_t | offsetY | ||

| ) |

| base | DPU peripheral base address. |

| unit | DPU unit, see dpu_unit_t, must be Store unit here. |

| offsetX | Horizontal offset. |

| offsetY | Vertical offset. |

| void DPU_StartStore | ( | IRIS_MVPL_Type * | base, |

| dpu_unit_t | unit | ||

| ) |

This function starts the Store unit to save the frame to output buffer. When the frame store completed, the interrupt flag kDPU_Group0Store9FrameCompleteInterrupt asserts.

This is an example shows how to use Store unit:

For better performance, it is allowed to set next operation while current is still in progress. Upper layer could set next operation immediately after shadow load finished.

| base | DPU peripheral base address. |

| unit | DPU unit, see dpu_unit_t, must be Store unit here. |

| void DPU_InitRop | ( | IRIS_MVPL_Type * | base, |

| dpu_unit_t | unit, | ||

| uint32_t | srcReg | ||

| ) |

The primary input source of the unit could be:

The secondary input source of the unit could be:

The tert input source of the unit could be:

| base | DPU peripheral base address. |

| unit | DPU unit, see dpu_unit_t, must be Rop unit here. |

| srcReg | Unit source selection, see DPU_MAKE_SRC_REG3. |

| void DPU_RopGetDefaultConfig | ( | dpu_rop_config_t * | config | ) |

The default configuration is:

| config | Pointer to the configuration structure. |

| void DPU_SetRopConfig | ( | IRIS_MVPL_Type * | base, |

| dpu_unit_t | unit, | ||

| const dpu_rop_config_t * | config | ||

| ) |

| base | DPU peripheral base address. |

| unit | DPU unit, see dpu_unit_t, must be Rop unit here. |

| config | Pointer to the configuration structure. |

| void DPU_EnableRop | ( | IRIS_MVPL_Type * | base, |

| dpu_unit_t | unit, | ||

| bool | enable | ||

| ) |

If disabled, only the primary input is output.

| base | DPU peripheral base address. |

| unit | DPU unit, see dpu_unit_t, must be Rop unit here. |

| enable | Pass true to enable, false to disable. |

| void DPU_InitBlitBlend | ( | IRIS_MVPL_Type * | base, |

| dpu_unit_t | unit, | ||

| uint32_t | srcReg | ||

| ) |

The valid input primary source could be:

The valid input secondary source could be:

| base | DPU peripheral base address. |

| unit | DPU unit, see dpu_unit_t, must be BlitBlend unit here. |

| srcReg | Unit source selection, see DPU_MAKE_SRC_REG2. |

| void DPU_BlitBlendGetDefaultConfig | ( | dpu_blit_blend_config_t * | config | ) |

The default configuration is:

| config | Pointer to the configuration structure. |

| void DPU_SetBlitBlendConfig | ( | IRIS_MVPL_Type * | base, |

| dpu_unit_t | unit, | ||

| const dpu_blit_blend_config_t * | config | ||

| ) |

| base | DPU peripheral base address. |

| unit | DPU unit, see dpu_unit_t, must be BlitBlend unit here. |

| config | Pointer to the configuration structure. |

| void DPU_EnableBlitBlend | ( | IRIS_MVPL_Type * | base, |

| dpu_unit_t | unit, | ||

| bool | enable | ||

| ) |

The BlitBlend unit could be runtime enabled or disabled, when disabled, the primary input is output directly.

| base | DPU peripheral base address. |

| unit | DPU unit, see dpu_unit_t, must be BlitBlend unit here. |

| enable | Pass true to enable, false to disable. |

| void DPU_LayerBlendGetDefaultConfig | ( | dpu_layer_blend_config_t * | config | ) |

The default value is:

| config | Pointer to the configuration structure. |

| void DPU_InitLayerBlend | ( | IRIS_MVPL_Type * | base, |

| dpu_unit_t | unit, | ||

| uint32_t | srcReg | ||

| ) |

The valid primary source:

The valid secondary source:

| base | DPU peripheral base address. |

| unit | DPU unit, see dpu_unit_t, must be LayerBlend unit here. |

| srcReg | Unit source selection, see DPU_MAKE_SRC_REG2. |

| void DPU_SetLayerBlendConfig | ( | IRIS_MVPL_Type * | base, |

| dpu_unit_t | unit, | ||

| const dpu_layer_blend_config_t * | config | ||

| ) |

| base | DPU peripheral base address. |

| unit | DPU unit, see dpu_unit_t, must be LayerBlend unit here. |

| config | Pointer to the configuration structure. |

| void DPU_EnableLayerBlend | ( | IRIS_MVPL_Type * | base, |

| dpu_unit_t | unit, | ||

| bool | enable | ||

| ) |

If enabled, the blend result is output, otherwise, the primary input is output.

| base | DPU peripheral base address. |

| unit | DPU unit, see dpu_unit_t, must be LayerBlend unit here. |

| enable | Pass true to enable, false to disable. |

| void DPU_InitConstFrame | ( | IRIS_MVPL_Type * | base, |

| dpu_unit_t | unit | ||

| ) |

| base | DPU peripheral base address. |

| unit | DPU unit, see dpu_unit_t, must be ConstFrame unit here. |

| void DPU_ConstFrameGetDefaultConfig | ( | dpu_const_frame_config_t * | config | ) |

The default value is:

| config | Pointer to the configuration structure. |

| void DPU_SetConstFrameConfig | ( | IRIS_MVPL_Type * | base, |

| dpu_unit_t | unit, | ||

| const dpu_const_frame_config_t * | config | ||

| ) |

| base | DPU peripheral base address. |

| unit | DPU unit, see dpu_unit_t, must be ConstFrame unit here. |

| config | Pointer to the configuration structure. |

| void DPU_InitScaler | ( | IRIS_MVPL_Type * | base, |

| dpu_unit_t | unit | ||

| ) |

| base | DPU peripheral base address. |

| unit | DPU unit, see dpu_unit_t, must be HScaler or VScaler unit here. |

| void DPU_ScalerGetDefaultConfig | ( | dpu_scaler_config_t * | config | ) |

The default value is:

| config | Pointer to the configuration structure. |

| void DPU_SetScalerConfig | ( | IRIS_MVPL_Type * | base, |

| dpu_unit_t | unit, | ||

| const dpu_scaler_config_t * | config | ||

| ) |

The valid input source could be:

| base | DPU peripheral base address. |

| unit | DPU unit, see dpu_unit_t, must be HScaler or VScaler unit here. |

| config | Pointer to the configuration structure. |

| void DPU_DisplayTimingGetDefaultConfig | ( | dpu_display_timing_config_t * | config | ) |

The default value is:

| config | Pointer to the configuration structure. |

| void DPU_InitDisplayTiming | ( | IRIS_MVPL_Type * | base, |

| uint8_t | displayIndex, | ||

| const dpu_display_timing_config_t * | config | ||

| ) |

| base | DPU peripheral base address. |

| displayIndex | Index of the display. |

| config | Pointer to the configuration structure. |

| void DPU_DisplayGetDefaultConfig | ( | dpu_display_config_t * | config | ) |

The default value is:

| config | Pointer to the configuration structure. |

| void DPU_SetDisplayConfig | ( | IRIS_MVPL_Type * | base, |

| uint8_t | displayIndex, | ||

| const dpu_display_config_t * | config | ||

| ) |

| base | DPU peripheral base address. |

| displayIndex | Index of the display. |

| config | Pointer to the configuration structure. |

| void DPU_StartDisplay | ( | IRIS_MVPL_Type * | base, |

| uint8_t | displayIndex | ||

| ) |

| base | DPU peripheral base address. |

| displayIndex | Index of the display. |

| void DPU_StopDisplay | ( | IRIS_MVPL_Type * | base, |

| uint8_t | displayIndex | ||

| ) |

This function stops the display and wait the sequence complete.

| base | DPU peripheral base address. |

| displayIndex | Index of the display. |

| void DPU_SetFrameGenInterruptConfig | ( | IRIS_MVPL_Type * | base, |

| uint8_t | displayIndex, | ||

| uint8_t | interruptIndex, | ||

| uint32_t | intConfig | ||

| ) |

| base | DPU peripheral base address. |

| displayIndex | Display index. |

| interruptIndex | Interrupt index, there could be 4 interrupts for each display. |

| intConfig | Interrupt mode, could be one of DPU_FRAME_GEN_INT_DISABLE, DPU_FRAME_GEN_INT_PER_LINE, and DPU_FRAME_GEN_INT_PER_FRAME. |

| void DPU_TriggerDisplayShadowLoad | ( | IRIS_MVPL_Type * | base, |

| uint8_t | displayIndex | ||

| ) |

Trigger the display stream shadow load token, then the shadow register will be loaded at the begining of next frame.

| base | DPU peripheral base address. |

| displayIndex | Display index. |

| void DPU_SignatureGetDefaultConfig | ( | dpu_signature_config_t * | config | ) |

The default configuration is:

| config | Pointer to the configuration. |

| void DPU_InitSignature | ( | IRIS_MVPL_Type * | base, |

| uint8_t | displayIndex, | ||

| const dpu_signature_config_t * | config | ||

| ) |

| base | DPU peripheral base address. |

| displayIndex | Display index. |

| config | Pointer to the configuration. |

| void DPU_SignatureWindowGetDefaultConfig | ( | dpu_signature_window_config_t * | config | ) |

The default configuration is:

| config | Pointer to the configuration. |

| void DPU_SetSignatureWindowConfig | ( | IRIS_MVPL_Type * | base, |

| uint8_t | displayIndex, | ||

| uint8_t | windowIndex, | ||

| const dpu_signature_window_config_t * | config | ||

| ) |

| base | DPU peripheral base address. |

| displayIndex | Display index. |

| windowIndex | Evaluation window index, should be 0 to 7. |

| config | Pointer to the configuration. |

| void DPU_EnableSignatureWindowCompute | ( | IRIS_MVPL_Type * | base, |

| uint8_t | displayIndex, | ||

| uint8_t | windowIndex, | ||

| bool | enable | ||

| ) |

When enabled, a CRC signature is computed for all pixels inside this evaluation window, When disabled, the internal status for this window is reset (StsSigError bit and frame counters)

| base | DPU peripheral base address. |

| displayIndex | Display index. |

| windowIndex | Evaluation window index, should be 0 to 7. |

| enable | Pass true to enable, false to disable. |

| void DPU_EnableSignatureWindowCheck | ( | IRIS_MVPL_Type * | base, |

| uint8_t | displayIndex, | ||

| uint8_t | windowIndex, | ||

| bool | enable | ||

| ) |

When enabled, the measured signature is checked against a reference value.

| base | DPU peripheral base address. |

| displayIndex | Display index. |

| windowIndex | Evaluation window index, should be 0 to 7. |

| enable | Pass true to enable, false to disable. |

| void DPU_GetSignatureWindowCrc | ( | IRIS_MVPL_Type * | base, |

| uint8_t | displayIndex, | ||

| uint8_t | windowIndex, | ||

| uint32_t * | redCRC, | ||

| uint32_t * | greenCRC, | ||

| uint32_t * | blueCRC | ||

| ) |

| base | DPU peripheral base address. |

| displayIndex | Display index. |

| windowIndex | Evaluation window index, should be 0 to 7. |

| redCRC | Measured signature value of red. |

| greenCRC | Measured signature value of green. |

| blueCRC | Measured signature value of blue. |

| void DPU_SetSignatureWindowRefCrc | ( | IRIS_MVPL_Type * | base, |

| uint8_t | displayIndex, | ||

| uint8_t | windowIndex, | ||

| uint32_t | redCRC, | ||

| uint32_t | greenCRC, | ||

| uint32_t | blueCRC | ||

| ) |

| base | DPU peripheral base address. |

| displayIndex | Display index. |

| windowIndex | Evaluation window index, should be 0 to 7. |

| redCRC | Reference signature value of red. |

| greenCRC | Referencesignature value of green. |

| blueCRC | Reference signature value of blue. |

| uint32_t DPU_GetSignatureStatus | ( | IRIS_MVPL_Type * | base, |

| uint8_t | displayIndex | ||

| ) |

This function returns the signature unit status. The return value could be compared to check the status defined in _dpu_signature_status. For example:

The error flags are also returned as an mask value, upper layer could get specific window status by checking the returned bit accordingly. For example,

| base | DPU peripheral base address. |

| displayIndex | Display index. |

| void DPU_TriggerSignatureShadowLoad | ( | IRIS_MVPL_Type * | base, |

| uint8_t | displayIndex | ||

| ) |

When new configuration set by DPU_SetSignatureWindowConfig, DPU_EnableSignatureWindowCheck, DPU_EnableSignatureWindowCompute, and DPU_SetSignatureWindowRefCrc, use this function to trigger the shadow load, then the new configuration takes effect.

Upper layer should monitor the kDPU_Group0Sig0ShadowLoadInterrupt or kDPU_Group1Sig1ShadowLoadInterrupt to wait shadow load finished. New configurations should only be set after shadow load finished.

| base | DPU peripheral base address. |

| displayIndex | Display index. |