|

ISSDK

1.7

IoT Sensing Software Development Kit

|

|

ISSDK

1.7

IoT Sensing Software Development Kit

|

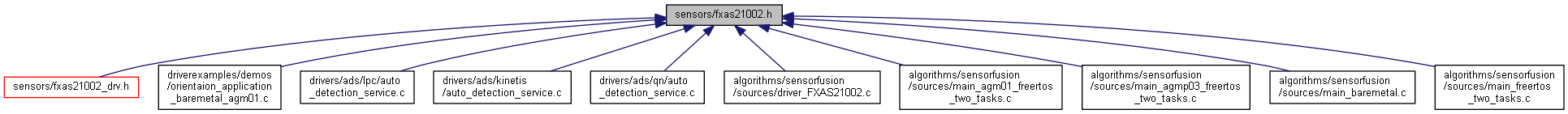

The fxas21002.h contains the fxas21002 sensor register definitions and its bit mask. More...

Go to the source code of this file.

Data Structures | |

| union | FXAS21002_DR_STATUS_t |

| union | FXAS21002_F_STATUS_t |

| union | FXAS21002_F_SETUP_t |

| union | FXAS21002_F_EVENT_t |

| union | FXAS21002_INT_SRC_FLAG_t |

| union | FXAS21002_WHO_AM_I_t |

| union | FXAS21002_CTRL_REG0_t |

| union | FXAS21002_RT_CFG_t |

| union | FXAS21002_RT_SRC_t |

| union | FXAS21002_RT_THS_t |

| union | FXAS21002_CTRL_REG1_t |

| union | FXAS21002_CTRL_REG2_t |

| union | FXAS21002_CTRL_REG3_t |

Macros | |

| #define | FXAS21002_I2C_ADDRESS 0x20 |

| #define | FXAS21002_DR_STATUS_XDR_MASK ((uint8_t) 0x01) |

| #define | FXAS21002_DR_STATUS_XDR_SHIFT ((uint8_t) 0) |

| #define | FXAS21002_DR_STATUS_YDR_MASK ((uint8_t) 0x02) |

| #define | FXAS21002_DR_STATUS_YDR_SHIFT ((uint8_t) 1) |

| #define | FXAS21002_DR_STATUS_ZDR_MASK ((uint8_t) 0x04) |

| #define | FXAS21002_DR_STATUS_ZDR_SHIFT ((uint8_t) 2) |

| #define | FXAS21002_DR_STATUS_ZYXDR_MASK ((uint8_t) 0x08) |

| #define | FXAS21002_DR_STATUS_ZYXDR_SHIFT ((uint8_t) 3) |

| #define | FXAS21002_DR_STATUS_XOW_MASK ((uint8_t) 0x10) |

| #define | FXAS21002_DR_STATUS_XOW_SHIFT ((uint8_t) 4) |

| #define | FXAS21002_DR_STATUS_YOW_MASK ((uint8_t) 0x20) |

| #define | FXAS21002_DR_STATUS_YOW_SHIFT ((uint8_t) 5) |

| #define | FXAS21002_DR_STATUS_ZOW_MASK ((uint8_t) 0x40) |

| #define | FXAS21002_DR_STATUS_ZOW_SHIFT ((uint8_t) 6) |

| #define | FXAS21002_DR_STATUS_ZYXOW_MASK ((uint8_t) 0x80) |

| #define | FXAS21002_DR_STATUS_ZYXOW_SHIFT ((uint8_t) 7) |

| #define | FXAS21002_DR_STATUS_XDR_DRDY ((uint8_t) 0x01) /* Set to 1 whenever a new X-axis data acquisition */ |

| #define | FXAS21002_DR_STATUS_YDR_DRDY ((uint8_t) 0x02) /* Set to 1 whenever a new Y-axis data acquisition */ |

| #define | FXAS21002_DR_STATUS_ZDR_DRDY ((uint8_t) 0x04) /* Set to 1 whenever a new Z-axis data acquisition */ |

| #define | FXAS21002_DR_STATUS_ZYXDR_DRDY ((uint8_t) 0x08) /* Cleared when the high-bytes of the acceleration */ |

| #define | FXAS21002_DR_STATUS_XOW_OWR ((uint8_t) 0x10) /* Asserted whenever a new X-axis acquisition is */ |

| #define | FXAS21002_DR_STATUS_YOW_OWR ((uint8_t) 0x20) /* Asserted whenever a new Y-axis acquisition is */ |

| #define | FXAS21002_DR_STATUS_ZOW_OWR ((uint8_t) 0x40) /* Asserted whenever a new Z-axis acquisition is */ |

| #define | FXAS21002_DR_STATUS_ZYXOW_OWR ((uint8_t) 0x80) /* Asserted whenever new X-, Y-, and Z-axis data is */ |

| #define | FXAS21002_F_STATUS_F_CNT_MASK ((uint8_t) 0x3F) |

| #define | FXAS21002_F_STATUS_F_CNT_SHIFT ((uint8_t) 0) |

| #define | FXAS21002_F_STATUS_F_WMKF_MASK ((uint8_t) 0x40) |

| #define | FXAS21002_F_STATUS_F_WMKF_SHIFT ((uint8_t) 6) |

| #define | FXAS21002_F_STATUS_F_OVF_MASK ((uint8_t) 0x80) |

| #define | FXAS21002_F_STATUS_F_OVF_SHIFT ((uint8_t) 7) |

| #define | FXAS21002_F_STATUS_F_WMKF_DETECT ((uint8_t) 0x40) /* FIFO Watermark event has been detected. */ |

| #define | FXAS21002_F_STATUS_F_OVF_DETECT ((uint8_t) 0x80) /* FIFO Overflow event has been detected. */ |

| #define | FXAS21002_F_SETUP_F_WMRK_MASK ((uint8_t) 0x3F) |

| #define | FXAS21002_F_SETUP_F_WMRK_SHIFT ((uint8_t) 0) |

| #define | FXAS21002_F_SETUP_F_MODE_MASK ((uint8_t) 0xC0) |

| #define | FXAS21002_F_SETUP_F_MODE_SHIFT ((uint8_t) 6) |

| #define | FXAS21002_F_SETUP_F_MODE_FIFO_OFF ((uint8_t) 0x00) /* FIFO is disabled. */ |

| #define | FXAS21002_F_SETUP_F_MODE_CIR_MODE ((uint8_t) 0x40) /* FIFO is in Circular Buffer mode. */ |

| #define | FXAS21002_F_SETUP_F_MODE_STOP_MODE ((uint8_t) 0x80) /* FIFO is in Stop mode. */ |

| #define | FXAS21002_F_EVENT_FE_TIME_MASK ((uint8_t) 0x1F) |

| #define | FXAS21002_F_EVENT_FE_TIME_SHIFT ((uint8_t) 0) |

| #define | FXAS21002_F_EVENT_F_EVENT_MASK ((uint8_t) 0x20) |

| #define | FXAS21002_F_EVENT_F_EVENT_SHIFT ((uint8_t) 5) |

| #define | FXAS21002_F_EVENT_F_EVENT_DETECTED ((uint8_t) 0x20) /* FIFO event was detected */ |

| #define | FXAS21002_INT_SRC_FLAG_SRC_DRDY_MASK ((uint8_t) 0x01) |

| #define | FXAS21002_INT_SRC_FLAG_SRC_DRDY_SHIFT ((uint8_t) 0) |

| #define | FXAS21002_INT_SRC_FLAG_SRC_RT_MASK ((uint8_t) 0x02) |

| #define | FXAS21002_INT_SRC_FLAG_SRC_RT_SHIFT ((uint8_t) 1) |

| #define | FXAS21002_INT_SRC_FLAG_SRC_FIFO_MASK ((uint8_t) 0x04) |

| #define | FXAS21002_INT_SRC_FLAG_SRC_FIFO_SHIFT ((uint8_t) 2) |

| #define | FXAS21002_INT_SRC_FLAG_BOOTEND_MASK ((uint8_t) 0x08) |

| #define | FXAS21002_INT_SRC_FLAG_BOOTEND_SHIFT ((uint8_t) 3) |

| #define | FXAS21002_INT_SRC_FLAG_SRC_DRDY_READY ((uint8_t) 0x01) /* Asserted whenever a data-ready event triggers */ |

| #define | FXAS21002_INT_SRC_FLAG_SRC_RT_THRESH ((uint8_t) 0x02) /* Indicates that the rate threshold event flag */ |

| #define | FXAS21002_INT_SRC_FLAG_SRC_FIFO_EVENT ((uint8_t) 0x04) /* F_OVF or F_WMKF are set, provided the FIFO */ |

| #define | FXAS21002_INT_SRC_FLAG_BOOTEND_BOOT_DONE ((uint8_t) 0x08) /* Boot sequence is complete. */ |

| #define | FXAS21002_WHO_AM_I_WHOAMI_MASK ((uint8_t) 0xFF) |

| #define | FXAS21002_WHO_AM_I_WHOAMI_SHIFT ((uint8_t) 0) |

| #define | FXAS21002_WHO_AM_I_WHOAMI_OLD_VALUE ((uint8_t) 0xd1) /* FXAS21000 */ |

| #define | FXAS21002_WHO_AM_I_WHOAMI_PRE_VALUE ((uint8_t) 0xd6) /* Engineering Samples */ |

| #define | FXAS21002_WHO_AM_I_WHOAMI_PROD_VALUE ((uint8_t) 0xd7) /* FXAS21002 Rev 2.1 (production) */ |

| #define | FXAS21002_CTRL_REG0_FS_MASK ((uint8_t) 0x03) |

| #define | FXAS21002_CTRL_REG0_FS_SHIFT ((uint8_t) 0) |

| #define | FXAS21002_CTRL_REG0_HPF_EN_MASK ((uint8_t) 0x04) |

| #define | FXAS21002_CTRL_REG0_HPF_EN_SHIFT ((uint8_t) 2) |

| #define | FXAS21002_CTRL_REG0_SEL_MASK ((uint8_t) 0x18) |

| #define | FXAS21002_CTRL_REG0_SEL_SHIFT ((uint8_t) 3) |

| #define | FXAS21002_CTRL_REG0_SPIW_MASK ((uint8_t) 0x20) |

| #define | FXAS21002_CTRL_REG0_SPIW_SHIFT ((uint8_t) 5) |

| #define | FXAS21002_CTRL_REG0_BW_MASK ((uint8_t) 0xC0) |

| #define | FXAS21002_CTRL_REG0_BW_SHIFT ((uint8_t) 6) |

| #define | FXAS21002_CTRL_REG0_FS_DPS2000 ((uint8_t) 0x00) /* 2000 degrees per second (4000 dps if CTRL_REG3 : */ |

| #define | FXAS21002_CTRL_REG0_FS_DPS1000 ((uint8_t) 0x01) /* 1000 degrees per second (2000 dps if CTRL_REG3 : */ |

| #define | FXAS21002_CTRL_REG0_FS_DPS500 ((uint8_t) 0x02) /* 500 degrees per second (1000 dps if CTRL_REG3 : */ |

| #define | FXAS21002_CTRL_REG0_FS_DPS250 ((uint8_t) 0x03) /* 250 degrees per second (500 dps if CTRL_REG3 : */ |

| #define | FXAS21002_CTRL_REG0_HPF_EN_ENABLE ((uint8_t) 0x04) |

| #define | FXAS21002_CTRL_REG0_HPF_EN_DISABLE ((uint8_t) 0x00) |

| #define | FXAS21002_CTRL_REG0_SPIW_4WIRE ((uint8_t) 0x00) /* SPI 4-wire mode (default). */ |

| #define | FXAS21002_CTRL_REG0_SPIW_3WIRE ((uint8_t) 0x20) /* SPI 3-wire mode (MOSI pin is used for SPI input */ |

| #define | FXAS21002_RT_CFG_XTEFE_MASK ((uint8_t) 0x01) |

| #define | FXAS21002_RT_CFG_XTEFE_SHIFT ((uint8_t) 0) |

| #define | FXAS21002_RT_CFG_YTEFE_MASK ((uint8_t) 0x02) |

| #define | FXAS21002_RT_CFG_YTEFE_SHIFT ((uint8_t) 1) |

| #define | FXAS21002_RT_CFG_ZTEFE_MASK ((uint8_t) 0x04) |

| #define | FXAS21002_RT_CFG_ZTEFE_SHIFT ((uint8_t) 2) |

| #define | FXAS21002_RT_CFG_ELE_MASK ((uint8_t) 0x08) |

| #define | FXAS21002_RT_CFG_ELE_SHIFT ((uint8_t) 3) |

| #define | FXAS21002_RT_CFG_XTEFE_ENABLE ((uint8_t) 0x01) /* X event detection enabled. */ |

| #define | FXAS21002_RT_CFG_XTEFE_DISABLE ((uint8_t) 0x00) /* X event detection disabled. */ |

| #define | FXAS21002_RT_CFG_YTEFE_ENABLE ((uint8_t) 0x02) /* Y event detection enabled. */ |

| #define | FXAS21002_RT_CFG_YTEFE_DISABLE ((uint8_t) 0x00) /* Y event detection disabled. */ |

| #define | FXAS21002_RT_CFG_ZTEFE_ENABLE ((uint8_t) 0x04) /* Z event detection enabled. */ |

| #define | FXAS21002_RT_CFG_ZTEFE_DISABLE ((uint8_t) 0x00) /* Z event detection disabled. */ |

| #define | FXAS21002_RT_CFG_ELE_ENABLE ((uint8_t) 0x08) /* Event flag latch enabled. */ |

| #define | FXAS21002_RT_CFG_ELE_DISABLE ((uint8_t) 0x00) /* Event flag latch disabled. */ |

| #define | FXAS21002_RT_SRC_X_RT_POL_MASK ((uint8_t) 0x01) |

| #define | FXAS21002_RT_SRC_X_RT_POL_SHIFT ((uint8_t) 0) |

| #define | FXAS21002_RT_SRC_XRT_MASK ((uint8_t) 0x02) |

| #define | FXAS21002_RT_SRC_XRT_SHIFT ((uint8_t) 1) |

| #define | FXAS21002_RT_SRC_Y_RT_POL_MASK ((uint8_t) 0x04) |

| #define | FXAS21002_RT_SRC_Y_RT_POL_SHIFT ((uint8_t) 2) |

| #define | FXAS21002_RT_SRC_YRT_MASK ((uint8_t) 0x08) |

| #define | FXAS21002_RT_SRC_YRT_SHIFT ((uint8_t) 3) |

| #define | FXAS21002_RT_SRC_Z_RT_POL_MASK ((uint8_t) 0x10) |

| #define | FXAS21002_RT_SRC_Z_RT_POL_SHIFT ((uint8_t) 4) |

| #define | FXAS21002_RT_SRC_ZRT_MASK ((uint8_t) 0x20) |

| #define | FXAS21002_RT_SRC_ZRT_SHIFT ((uint8_t) 5) |

| #define | FXAS21002_RT_SRC_EA_MASK ((uint8_t) 0x40) |

| #define | FXAS21002_RT_SRC_EA_SHIFT ((uint8_t) 6) |

| #define | FXAS21002_RT_SRC_X_RT_POL_POS ((uint8_t) 0x00) /* Rate Event was Positive. */ |

| #define | FXAS21002_RT_SRC_X_RT_POL_NEG ((uint8_t) 0x01) /* Rate Event was Negative. */ |

| #define | FXAS21002_RT_SRC_XRT_LOWER ((uint8_t) 0x00) /* Rate lower than RT_THS value. */ |

| #define | FXAS21002_RT_SRC_XRT_GREATER ((uint8_t) 0x02) /* Rate greater than RT_THS value. Event has occured. */ |

| #define | FXAS21002_RT_SRC_Y_RT_POL_POS ((uint8_t) 0x00) /* Rate Event was Positive. */ |

| #define | FXAS21002_RT_SRC_Y_RT_POL_NEG ((uint8_t) 0x04) /* Rate Event was Negative. */ |

| #define | FXAS21002_RT_SRC_YRT_LOWER ((uint8_t) 0x00) /* Rate lower than RT_THS value. */ |

| #define | FXAS21002_RT_SRC_YRT_GREATER ((uint8_t) 0x08) /* Rate greater than RT_THS value. Event has occured. */ |

| #define | FXAS21002_RT_SRC_Z_RT_POL_POS ((uint8_t) 0x00) /* Rate Event was Positive. */ |

| #define | FXAS21002_RT_SRC_Z_RT_POL_NEG ((uint8_t) 0x10) /* Rate Event was Negative. */ |

| #define | FXAS21002_RT_SRC_ZRT_LOWER ((uint8_t) 0x00) /* Rate lower than RT_THS value. */ |

| #define | FXAS21002_RT_SRC_ZRT_GREATER ((uint8_t) 0x20) /* Rate greater than RT_THS value. Event has occured. */ |

| #define | FXAS21002_RT_SRC_EA_NOEVENT ((uint8_t) 0x00) /* No event flags have been asserted. */ |

| #define | FXAS21002_RT_SRC_EA_EVENT ((uint8_t) 0x40) /* One or more event flags have been asserted. */ |

| #define | FXAS21002_RT_THS_THS_MASK ((uint8_t) 0x7F) |

| #define | FXAS21002_RT_THS_THS_SHIFT ((uint8_t) 0) |

| #define | FXAS21002_RT_THS_DBCNTM_MASK ((uint8_t) 0x80) |

| #define | FXAS21002_RT_THS_DBCNTM_SHIFT ((uint8_t) 7) |

| #define | FXAS21002_RT_THS_DBCNTM_CLEAR ((uint8_t) 0x80) /* Clear counter when angular rate is below the */ |

| #define | FXAS21002_RT_THS_DBCNTM_DECREMENT ((uint8_t) 0x00) /* Decrement counter on every ODR cycle that the */ |

| #define | FXAS21002_CTRL_REG1_MODE_MASK ((uint8_t) 0x03) |

| #define | FXAS21002_CTRL_REG1_MODE_SHIFT ((uint8_t) 0) |

| #define | FXAS21002_CTRL_REG1_DR_MASK ((uint8_t) 0x1C) |

| #define | FXAS21002_CTRL_REG1_DR_SHIFT ((uint8_t) 2) |

| #define | FXAS21002_CTRL_REG1_ST_MASK ((uint8_t) 0x20) |

| #define | FXAS21002_CTRL_REG1_ST_SHIFT ((uint8_t) 5) |

| #define | FXAS21002_CTRL_REG1_RST_MASK ((uint8_t) 0x40) |

| #define | FXAS21002_CTRL_REG1_RST_SHIFT ((uint8_t) 6) |

| #define | FXAS21002_CTRL_REG1_MODE_STANDBY ((uint8_t) 0x00) /* Standby Mode. Register setting allowed. Lowest */ |

| #define | FXAS21002_CTRL_REG1_MODE_READY ((uint8_t) 0x01) /* Ready Mode. The device is ready to measure */ |

| #define | FXAS21002_CTRL_REG1_MODE_ACTIVE ((uint8_t) 0x02) /* Active Mode. The device is fully functional. */ |

| #define | FXAS21002_CTRL_REG1_DR_800HZ ((uint8_t) 0x00) |

| #define | FXAS21002_CTRL_REG1_DR_400HZ ((uint8_t) 0x04) |

| #define | FXAS21002_CTRL_REG1_DR_200HZ ((uint8_t) 0x08) |

| #define | FXAS21002_CTRL_REG1_DR_100HZ ((uint8_t) 0x0c) |

| #define | FXAS21002_CTRL_REG1_DR_50HZ ((uint8_t) 0x10) |

| #define | FXAS21002_CTRL_REG1_DR_25HZ ((uint8_t) 0x14) |

| #define | FXAS21002_CTRL_REG1_DR_12_5HZ ((uint8_t) 0x18) |

| #define | FXAS21002_CTRL_REG1_ST_ENABLE ((uint8_t) 0x20) |

| #define | FXAS21002_CTRL_REG1_ST_DISABLE ((uint8_t) 0x00) |

| #define | FXAS21002_CTRL_REG1_RST_TRIGGER ((uint8_t) 0x40) |

| #define | FXAS21002_CTRL_REG1_RST_NOTTRIGGERED ((uint8_t) 0x00) |

| #define | FXAS21002_CTRL_REG2_PP_OD_MASK ((uint8_t) 0x01) |

| #define | FXAS21002_CTRL_REG2_PP_OD_SHIFT ((uint8_t) 0) |

| #define | FXAS21002_CTRL_REG2_IPOL_MASK ((uint8_t) 0x02) |

| #define | FXAS21002_CTRL_REG2_IPOL_SHIFT ((uint8_t) 1) |

| #define | FXAS21002_CTRL_REG2_INT_EN_DRDY_MASK ((uint8_t) 0x04) |

| #define | FXAS21002_CTRL_REG2_INT_EN_DRDY_SHIFT ((uint8_t) 2) |

| #define | FXAS21002_CTRL_REG2_INT_CFG_DRDY_MASK ((uint8_t) 0x08) |

| #define | FXAS21002_CTRL_REG2_INT_CFG_DRDY_SHIFT ((uint8_t) 3) |

| #define | FXAS21002_CTRL_REG2_INT_EN_RT_MASK ((uint8_t) 0x10) |

| #define | FXAS21002_CTRL_REG2_INT_EN_RT_SHIFT ((uint8_t) 4) |

| #define | FXAS21002_CTRL_REG2_INT_CFG_RT_MASK ((uint8_t) 0x20) |

| #define | FXAS21002_CTRL_REG2_INT_CFG_RT_SHIFT ((uint8_t) 5) |

| #define | FXAS21002_CTRL_REG2_INT_EN_FIFO_MASK ((uint8_t) 0x40) |

| #define | FXAS21002_CTRL_REG2_INT_EN_FIFO_SHIFT ((uint8_t) 6) |

| #define | FXAS21002_CTRL_REG2_INT_CFG_FIFO_MASK ((uint8_t) 0x80) |

| #define | FXAS21002_CTRL_REG2_INT_CFG_FIFO_SHIFT ((uint8_t) 7) |

| #define | FXAS21002_CTRL_REG2_PP_OD_PUSHPULL ((uint8_t) 0x00) /* Push-pull output driver. */ |

| #define | FXAS21002_CTRL_REG2_PP_OD_OPENDRAIN ((uint8_t) 0x01) /* Open-drain output driver. */ |

| #define | FXAS21002_CTRL_REG2_IPOL_ACTIVE_LOW ((uint8_t) 0x00) |

| #define | FXAS21002_CTRL_REG2_IPOL_ACTIVE_HIGH ((uint8_t) 0x02) |

| #define | FXAS21002_CTRL_REG2_INT_EN_DRDY_ENABLE ((uint8_t) 0x04) |

| #define | FXAS21002_CTRL_REG2_INT_EN_DRDY_DISABLE ((uint8_t) 0x00) |

| #define | FXAS21002_CTRL_REG2_INT_CFG_DRDY_INT2 ((uint8_t) 0x00) /* Interrupt is routed to INT2 pin. */ |

| #define | FXAS21002_CTRL_REG2_INT_CFG_DRDY_INT1 ((uint8_t) 0x08) /* Interrupt is routed to INT1 pin. */ |

| #define | FXAS21002_CTRL_REG2_INT_EN_RT_ENABLE ((uint8_t) 0x10) |

| #define | FXAS21002_CTRL_REG2_INT_EN_RT_DISABLE ((uint8_t) 0x00) |

| #define | FXAS21002_CTRL_REG2_INT_CFG_RT_INT2 ((uint8_t) 0x00) /* Interrupt is routed to INT2 pin. */ |

| #define | FXAS21002_CTRL_REG2_INT_CFG_RT_INT1 ((uint8_t) 0x20) /* Interrupt is routed to INT1 pin. */ |

| #define | FXAS21002_CTRL_REG2_INT_EN_FIFO_ENABLE ((uint8_t) 0x40) |

| #define | FXAS21002_CTRL_REG2_INT_EN_FIFO_DISABLE ((uint8_t) 0x00) |

| #define | FXAS21002_CTRL_REG2_INT_CFG_FIFO_INT2 ((uint8_t) 0x00) /* Interrupt is routed to INT2 pin. */ |

| #define | FXAS21002_CTRL_REG2_INT_CFG_FIFO_INT1 ((uint8_t) 0x80) /* Interrupt is routed to INT1 pin. */ |

| #define | FXAS21002_CTRL_REG3_FS_DOUBLE_MASK ((uint8_t) 0x01) |

| #define | FXAS21002_CTRL_REG3_FS_DOUBLE_SHIFT ((uint8_t) 0) |

| #define | FXAS21002_CTRL_REG3_EXTCTRLEN_MASK ((uint8_t) 0x04) |

| #define | FXAS21002_CTRL_REG3_EXTCTRLEN_SHIFT ((uint8_t) 2) |

| #define | FXAS21002_CTRL_REG3_WRAPTOONE_MASK ((uint8_t) 0x08) |

| #define | FXAS21002_CTRL_REG3_WRAPTOONE_SHIFT ((uint8_t) 3) |

| #define | FXAS21002_CTRL_REG3_FS_DOUBLE_ENABLE ((uint8_t) 0x01) /* Maximum full-scale range selections are doubled */ |

| #define | FXAS21002_CTRL_REG3_FS_DOUBLE_DISABLE ((uint8_t) 0x00) /* Maximum full-scale range selections are as per */ |

| #define | FXAS21002_CTRL_REG3_EXTCTRLEN_INT2 ((uint8_t) 0x00) /* INT2 pin is used as an interrupt output */ |

| #define | FXAS21002_CTRL_REG3_EXTCTRLEN_POWER_CONTROL ((uint8_t) 0x04) /* INT2 pin becomes an input pin that may be used */ |

| #define | FXAS21002_CTRL_REG3_WRAPTOONE_ROLL_STATUS ((uint8_t) 0x00) /* The auto-increment read address pointer rolls */ |

| #define | FXAS21002_CTRL_REG3_WRAPTOONE_ROLL_DATA ((uint8_t) 0x08) /* The auto-increment pointer rolls over to address */ |

Typedefs | |

| typedef uint8_t | FXAS21002_STATUS_t |

| typedef uint8_t | FXAS21002_OUT_X_MSB_t |

| typedef uint8_t | FXAS21002_OUT_X_LSB_t |

| typedef uint8_t | FXAS21002_OUT_Y_MSB_t |

| typedef uint8_t | FXAS21002_OUT_Y_LSB_t |

| typedef uint8_t | FXAS21002_OUT_Z_MSB_t |

| typedef uint8_t | FXAS21002_OUT_Z_LSB_t |

| typedef uint8_t | FXAS21002_RT_COUNT_t |

| typedef uint8_t | FXAS21002_TEMP_t |

Enumerations | |

| enum | { FXAS21002_STATUS = 0x00, FXAS21002_OUT_X_MSB = 0x01, FXAS21002_OUT_X_LSB = 0x02, FXAS21002_OUT_Y_MSB = 0x03, FXAS21002_OUT_Y_LSB = 0x04, FXAS21002_OUT_Z_MSB = 0x05, FXAS21002_OUT_Z_LSB = 0x06, FXAS21002_DR_STATUS = 0x07, FXAS21002_F_STATUS = 0x08, FXAS21002_F_SETUP = 0x09, FXAS21002_F_EVENT = 0x0A, FXAS21002_INT_SRC_FLAG = 0x0B, FXAS21002_WHO_AM_I = 0x0C, FXAS21002_CTRL_REG0 = 0x0D, FXAS21002_RT_CFG = 0x0E, FXAS21002_RT_SRC = 0x0F, FXAS21002_RT_THS = 0x10, FXAS21002_RT_COUNT = 0x11, FXAS21002_TEMP = 0x12, FXAS21002_CTRL_REG1 = 0x13, FXAS21002_CTRL_REG2 = 0x14, FXAS21002_CTRL_REG3 = 0x15 } |

| The FXAS21002 Sensor Register Map. More... | |

The fxas21002.h contains the fxas21002 sensor register definitions and its bit mask.

Definition in file fxas21002.h.

| #define FXAS21002_CTRL_REG0_BW_MASK ((uint8_t) 0xC0) |

Definition at line 473 of file fxas21002.h.

| #define FXAS21002_CTRL_REG0_BW_SHIFT ((uint8_t) 6) |

Definition at line 474 of file fxas21002.h.

| #define FXAS21002_CTRL_REG0_FS_DPS1000 ((uint8_t) 0x01) /* 1000 degrees per second (2000 dps if CTRL_REG3 : */ |

Definition at line 482 of file fxas21002.h.

| #define FXAS21002_CTRL_REG0_FS_DPS2000 ((uint8_t) 0x00) /* 2000 degrees per second (4000 dps if CTRL_REG3 : */ |

Definition at line 480 of file fxas21002.h.

| #define FXAS21002_CTRL_REG0_FS_DPS250 ((uint8_t) 0x03) /* 250 degrees per second (500 dps if CTRL_REG3 : */ |

Definition at line 486 of file fxas21002.h.

| #define FXAS21002_CTRL_REG0_FS_DPS500 ((uint8_t) 0x02) /* 500 degrees per second (1000 dps if CTRL_REG3 : */ |

Definition at line 484 of file fxas21002.h.

| #define FXAS21002_CTRL_REG0_FS_MASK ((uint8_t) 0x03) |

Definition at line 461 of file fxas21002.h.

| #define FXAS21002_CTRL_REG0_FS_SHIFT ((uint8_t) 0) |

Definition at line 462 of file fxas21002.h.

| #define FXAS21002_CTRL_REG0_HPF_EN_DISABLE ((uint8_t) 0x00) |

Definition at line 489 of file fxas21002.h.

| #define FXAS21002_CTRL_REG0_HPF_EN_ENABLE ((uint8_t) 0x04) |

Definition at line 488 of file fxas21002.h.

| #define FXAS21002_CTRL_REG0_HPF_EN_MASK ((uint8_t) 0x04) |

Definition at line 464 of file fxas21002.h.

| #define FXAS21002_CTRL_REG0_HPF_EN_SHIFT ((uint8_t) 2) |

Definition at line 465 of file fxas21002.h.

| #define FXAS21002_CTRL_REG0_SEL_MASK ((uint8_t) 0x18) |

Definition at line 467 of file fxas21002.h.

| #define FXAS21002_CTRL_REG0_SEL_SHIFT ((uint8_t) 3) |

Definition at line 468 of file fxas21002.h.

| #define FXAS21002_CTRL_REG0_SPIW_3WIRE ((uint8_t) 0x20) /* SPI 3-wire mode (MOSI pin is used for SPI input */ |

Definition at line 491 of file fxas21002.h.

| #define FXAS21002_CTRL_REG0_SPIW_4WIRE ((uint8_t) 0x00) /* SPI 4-wire mode (default). */ |

Definition at line 490 of file fxas21002.h.

| #define FXAS21002_CTRL_REG0_SPIW_MASK ((uint8_t) 0x20) |

Definition at line 470 of file fxas21002.h.

| #define FXAS21002_CTRL_REG0_SPIW_SHIFT ((uint8_t) 5) |

Definition at line 471 of file fxas21002.h.

| #define FXAS21002_CTRL_REG1_DR_100HZ ((uint8_t) 0x0c) |

Definition at line 733 of file fxas21002.h.

| #define FXAS21002_CTRL_REG1_DR_12_5HZ ((uint8_t) 0x18) |

Definition at line 736 of file fxas21002.h.

| #define FXAS21002_CTRL_REG1_DR_200HZ ((uint8_t) 0x08) |

Definition at line 732 of file fxas21002.h.

| #define FXAS21002_CTRL_REG1_DR_25HZ ((uint8_t) 0x14) |

Definition at line 735 of file fxas21002.h.

| #define FXAS21002_CTRL_REG1_DR_400HZ ((uint8_t) 0x04) |

Definition at line 731 of file fxas21002.h.

| #define FXAS21002_CTRL_REG1_DR_50HZ ((uint8_t) 0x10) |

Definition at line 734 of file fxas21002.h.

| #define FXAS21002_CTRL_REG1_DR_800HZ ((uint8_t) 0x00) |

Definition at line 730 of file fxas21002.h.

| #define FXAS21002_CTRL_REG1_DR_MASK ((uint8_t) 0x1C) |

Definition at line 710 of file fxas21002.h.

| #define FXAS21002_CTRL_REG1_DR_SHIFT ((uint8_t) 2) |

Definition at line 711 of file fxas21002.h.

| #define FXAS21002_CTRL_REG1_MODE_ACTIVE ((uint8_t) 0x02) /* Active Mode. The device is fully functional. */ |

Definition at line 728 of file fxas21002.h.

Referenced by FXAS21002_I2C_Configure(), and FXAS21002_SPI_Configure().

| #define FXAS21002_CTRL_REG1_MODE_MASK ((uint8_t) 0x03) |

Definition at line 707 of file fxas21002.h.

Referenced by FXAS21002_I2C_Configure(), and FXAS21002_SPI_Configure().

| #define FXAS21002_CTRL_REG1_MODE_READY ((uint8_t) 0x01) /* Ready Mode. The device is ready to measure */ |

Definition at line 725 of file fxas21002.h.

| #define FXAS21002_CTRL_REG1_MODE_SHIFT ((uint8_t) 0) |

Definition at line 708 of file fxas21002.h.

| #define FXAS21002_CTRL_REG1_MODE_STANDBY ((uint8_t) 0x00) /* Standby Mode. Register setting allowed. Lowest */ |

Definition at line 723 of file fxas21002.h.

Referenced by FXAS21002_I2C_Configure(), and FXAS21002_SPI_Configure().

| #define FXAS21002_CTRL_REG1_RST_MASK ((uint8_t) 0x40) |

Definition at line 716 of file fxas21002.h.

Referenced by FXAS21002_I2C_Deinit(), and FXAS21002_SPI_Deinit().

| #define FXAS21002_CTRL_REG1_RST_NOTTRIGGERED ((uint8_t) 0x00) |

Definition at line 740 of file fxas21002.h.

| #define FXAS21002_CTRL_REG1_RST_SHIFT ((uint8_t) 6) |

Definition at line 717 of file fxas21002.h.

| #define FXAS21002_CTRL_REG1_RST_TRIGGER ((uint8_t) 0x40) |

Definition at line 739 of file fxas21002.h.

Referenced by FXAS21002_I2C_Deinit(), and FXAS21002_SPI_Deinit().

| #define FXAS21002_CTRL_REG1_ST_DISABLE ((uint8_t) 0x00) |

Definition at line 738 of file fxas21002.h.

| #define FXAS21002_CTRL_REG1_ST_ENABLE ((uint8_t) 0x20) |

Definition at line 737 of file fxas21002.h.

| #define FXAS21002_CTRL_REG1_ST_MASK ((uint8_t) 0x20) |

Definition at line 713 of file fxas21002.h.

| #define FXAS21002_CTRL_REG1_ST_SHIFT ((uint8_t) 5) |

Definition at line 714 of file fxas21002.h.

| #define FXAS21002_CTRL_REG2_INT_CFG_DRDY_INT1 ((uint8_t) 0x08) /* Interrupt is routed to INT1 pin. */ |

Definition at line 812 of file fxas21002.h.

| #define FXAS21002_CTRL_REG2_INT_CFG_DRDY_INT2 ((uint8_t) 0x00) /* Interrupt is routed to INT2 pin. */ |

Definition at line 811 of file fxas21002.h.

| #define FXAS21002_CTRL_REG2_INT_CFG_DRDY_MASK ((uint8_t) 0x08) |

Definition at line 786 of file fxas21002.h.

| #define FXAS21002_CTRL_REG2_INT_CFG_DRDY_SHIFT ((uint8_t) 3) |

Definition at line 787 of file fxas21002.h.

| #define FXAS21002_CTRL_REG2_INT_CFG_FIFO_INT1 ((uint8_t) 0x80) /* Interrupt is routed to INT1 pin. */ |

Definition at line 820 of file fxas21002.h.

| #define FXAS21002_CTRL_REG2_INT_CFG_FIFO_INT2 ((uint8_t) 0x00) /* Interrupt is routed to INT2 pin. */ |

Definition at line 819 of file fxas21002.h.

| #define FXAS21002_CTRL_REG2_INT_CFG_FIFO_MASK ((uint8_t) 0x80) |

Definition at line 798 of file fxas21002.h.

| #define FXAS21002_CTRL_REG2_INT_CFG_FIFO_SHIFT ((uint8_t) 7) |

Definition at line 799 of file fxas21002.h.

| #define FXAS21002_CTRL_REG2_INT_CFG_RT_INT1 ((uint8_t) 0x20) /* Interrupt is routed to INT1 pin. */ |

Definition at line 816 of file fxas21002.h.

| #define FXAS21002_CTRL_REG2_INT_CFG_RT_INT2 ((uint8_t) 0x00) /* Interrupt is routed to INT2 pin. */ |

Definition at line 815 of file fxas21002.h.

| #define FXAS21002_CTRL_REG2_INT_CFG_RT_MASK ((uint8_t) 0x20) |

Definition at line 792 of file fxas21002.h.

| #define FXAS21002_CTRL_REG2_INT_CFG_RT_SHIFT ((uint8_t) 5) |

Definition at line 793 of file fxas21002.h.

| #define FXAS21002_CTRL_REG2_INT_EN_DRDY_DISABLE ((uint8_t) 0x00) |

Definition at line 810 of file fxas21002.h.

| #define FXAS21002_CTRL_REG2_INT_EN_DRDY_ENABLE ((uint8_t) 0x04) |

Definition at line 809 of file fxas21002.h.

| #define FXAS21002_CTRL_REG2_INT_EN_DRDY_MASK ((uint8_t) 0x04) |

Definition at line 783 of file fxas21002.h.

| #define FXAS21002_CTRL_REG2_INT_EN_DRDY_SHIFT ((uint8_t) 2) |

Definition at line 784 of file fxas21002.h.

| #define FXAS21002_CTRL_REG2_INT_EN_FIFO_DISABLE ((uint8_t) 0x00) |

Definition at line 818 of file fxas21002.h.

| #define FXAS21002_CTRL_REG2_INT_EN_FIFO_ENABLE ((uint8_t) 0x40) |

Definition at line 817 of file fxas21002.h.

| #define FXAS21002_CTRL_REG2_INT_EN_FIFO_MASK ((uint8_t) 0x40) |

Definition at line 795 of file fxas21002.h.

| #define FXAS21002_CTRL_REG2_INT_EN_FIFO_SHIFT ((uint8_t) 6) |

Definition at line 796 of file fxas21002.h.

| #define FXAS21002_CTRL_REG2_INT_EN_RT_DISABLE ((uint8_t) 0x00) |

Definition at line 814 of file fxas21002.h.

| #define FXAS21002_CTRL_REG2_INT_EN_RT_ENABLE ((uint8_t) 0x10) |

Definition at line 813 of file fxas21002.h.

| #define FXAS21002_CTRL_REG2_INT_EN_RT_MASK ((uint8_t) 0x10) |

Definition at line 789 of file fxas21002.h.

| #define FXAS21002_CTRL_REG2_INT_EN_RT_SHIFT ((uint8_t) 4) |

Definition at line 790 of file fxas21002.h.

| #define FXAS21002_CTRL_REG2_IPOL_ACTIVE_HIGH ((uint8_t) 0x02) |

Definition at line 808 of file fxas21002.h.

| #define FXAS21002_CTRL_REG2_IPOL_ACTIVE_LOW ((uint8_t) 0x00) |

Definition at line 807 of file fxas21002.h.

| #define FXAS21002_CTRL_REG2_IPOL_MASK ((uint8_t) 0x02) |

Definition at line 780 of file fxas21002.h.

| #define FXAS21002_CTRL_REG2_IPOL_SHIFT ((uint8_t) 1) |

Definition at line 781 of file fxas21002.h.

| #define FXAS21002_CTRL_REG2_PP_OD_MASK ((uint8_t) 0x01) |

Definition at line 777 of file fxas21002.h.

| #define FXAS21002_CTRL_REG2_PP_OD_OPENDRAIN ((uint8_t) 0x01) /* Open-drain output driver. */ |

Definition at line 806 of file fxas21002.h.

| #define FXAS21002_CTRL_REG2_PP_OD_PUSHPULL ((uint8_t) 0x00) /* Push-pull output driver. */ |

Definition at line 805 of file fxas21002.h.

| #define FXAS21002_CTRL_REG2_PP_OD_SHIFT ((uint8_t) 0) |

Definition at line 778 of file fxas21002.h.

| #define FXAS21002_CTRL_REG3_EXTCTRLEN_INT2 ((uint8_t) 0x00) /* INT2 pin is used as an interrupt output */ |

Definition at line 867 of file fxas21002.h.

| #define FXAS21002_CTRL_REG3_EXTCTRLEN_MASK ((uint8_t) 0x04) |

Definition at line 852 of file fxas21002.h.

| #define FXAS21002_CTRL_REG3_EXTCTRLEN_POWER_CONTROL ((uint8_t) 0x04) /* INT2 pin becomes an input pin that may be used */ |

Definition at line 869 of file fxas21002.h.

| #define FXAS21002_CTRL_REG3_EXTCTRLEN_SHIFT ((uint8_t) 2) |

Definition at line 853 of file fxas21002.h.

| #define FXAS21002_CTRL_REG3_FS_DOUBLE_DISABLE ((uint8_t) 0x00) /* Maximum full-scale range selections are as per */ |

Definition at line 864 of file fxas21002.h.

| #define FXAS21002_CTRL_REG3_FS_DOUBLE_ENABLE ((uint8_t) 0x01) /* Maximum full-scale range selections are doubled */ |

Definition at line 862 of file fxas21002.h.

| #define FXAS21002_CTRL_REG3_FS_DOUBLE_MASK ((uint8_t) 0x01) |

Definition at line 849 of file fxas21002.h.

| #define FXAS21002_CTRL_REG3_FS_DOUBLE_SHIFT ((uint8_t) 0) |

Definition at line 850 of file fxas21002.h.

| #define FXAS21002_CTRL_REG3_WRAPTOONE_MASK ((uint8_t) 0x08) |

Definition at line 855 of file fxas21002.h.

| #define FXAS21002_CTRL_REG3_WRAPTOONE_ROLL_DATA ((uint8_t) 0x08) /* The auto-increment pointer rolls over to address */ |

Definition at line 874 of file fxas21002.h.

| #define FXAS21002_CTRL_REG3_WRAPTOONE_ROLL_STATUS ((uint8_t) 0x00) /* The auto-increment read address pointer rolls */ |

Definition at line 871 of file fxas21002.h.

| #define FXAS21002_CTRL_REG3_WRAPTOONE_SHIFT ((uint8_t) 3) |

Definition at line 856 of file fxas21002.h.

| #define FXAS21002_DR_STATUS_XDR_DRDY ((uint8_t) 0x01) /* Set to 1 whenever a new X-axis data acquisition */ |

Definition at line 205 of file fxas21002.h.

| #define FXAS21002_DR_STATUS_XDR_MASK ((uint8_t) 0x01) |

Definition at line 177 of file fxas21002.h.

| #define FXAS21002_DR_STATUS_XDR_SHIFT ((uint8_t) 0) |

Definition at line 178 of file fxas21002.h.

| #define FXAS21002_DR_STATUS_XOW_MASK ((uint8_t) 0x10) |

Definition at line 189 of file fxas21002.h.

| #define FXAS21002_DR_STATUS_XOW_OWR ((uint8_t) 0x10) /* Asserted whenever a new X-axis acquisition is */ |

Definition at line 216 of file fxas21002.h.

| #define FXAS21002_DR_STATUS_XOW_SHIFT ((uint8_t) 4) |

Definition at line 190 of file fxas21002.h.

| #define FXAS21002_DR_STATUS_YDR_DRDY ((uint8_t) 0x02) /* Set to 1 whenever a new Y-axis data acquisition */ |

Definition at line 208 of file fxas21002.h.

| #define FXAS21002_DR_STATUS_YDR_MASK ((uint8_t) 0x02) |

Definition at line 180 of file fxas21002.h.

| #define FXAS21002_DR_STATUS_YDR_SHIFT ((uint8_t) 1) |

Definition at line 181 of file fxas21002.h.

| #define FXAS21002_DR_STATUS_YOW_MASK ((uint8_t) 0x20) |

Definition at line 192 of file fxas21002.h.

| #define FXAS21002_DR_STATUS_YOW_OWR ((uint8_t) 0x20) /* Asserted whenever a new Y-axis acquisition is */ |

Definition at line 219 of file fxas21002.h.

| #define FXAS21002_DR_STATUS_YOW_SHIFT ((uint8_t) 5) |

Definition at line 193 of file fxas21002.h.

| #define FXAS21002_DR_STATUS_ZDR_DRDY ((uint8_t) 0x04) /* Set to 1 whenever a new Z-axis data acquisition */ |

Definition at line 211 of file fxas21002.h.

| #define FXAS21002_DR_STATUS_ZDR_MASK ((uint8_t) 0x04) |

Definition at line 183 of file fxas21002.h.

| #define FXAS21002_DR_STATUS_ZDR_SHIFT ((uint8_t) 2) |

Definition at line 184 of file fxas21002.h.

| #define FXAS21002_DR_STATUS_ZOW_MASK ((uint8_t) 0x40) |

Definition at line 195 of file fxas21002.h.

| #define FXAS21002_DR_STATUS_ZOW_OWR ((uint8_t) 0x40) /* Asserted whenever a new Z-axis acquisition is */ |

Definition at line 222 of file fxas21002.h.

| #define FXAS21002_DR_STATUS_ZOW_SHIFT ((uint8_t) 6) |

Definition at line 196 of file fxas21002.h.

| #define FXAS21002_DR_STATUS_ZYXDR_DRDY ((uint8_t) 0x08) /* Cleared when the high-bytes of the acceleration */ |

Definition at line 214 of file fxas21002.h.

| #define FXAS21002_DR_STATUS_ZYXDR_MASK ((uint8_t) 0x08) |

Definition at line 186 of file fxas21002.h.

Referenced by main().

| #define FXAS21002_DR_STATUS_ZYXDR_SHIFT ((uint8_t) 3) |

Definition at line 187 of file fxas21002.h.

| #define FXAS21002_DR_STATUS_ZYXOW_MASK ((uint8_t) 0x80) |

Definition at line 198 of file fxas21002.h.

| #define FXAS21002_DR_STATUS_ZYXOW_OWR ((uint8_t) 0x80) /* Asserted whenever new X-, Y-, and Z-axis data is */ |

Definition at line 225 of file fxas21002.h.

| #define FXAS21002_DR_STATUS_ZYXOW_SHIFT ((uint8_t) 7) |

Definition at line 199 of file fxas21002.h.

| #define FXAS21002_F_EVENT_F_EVENT_DETECTED ((uint8_t) 0x20) /* FIFO event was detected */ |

Definition at line 344 of file fxas21002.h.

| #define FXAS21002_F_EVENT_F_EVENT_MASK ((uint8_t) 0x20) |

Definition at line 337 of file fxas21002.h.

Referenced by main().

| #define FXAS21002_F_EVENT_F_EVENT_SHIFT ((uint8_t) 5) |

Definition at line 338 of file fxas21002.h.

| #define FXAS21002_F_EVENT_FE_TIME_MASK ((uint8_t) 0x1F) |

Definition at line 334 of file fxas21002.h.

| #define FXAS21002_F_EVENT_FE_TIME_SHIFT ((uint8_t) 0) |

Definition at line 335 of file fxas21002.h.

| #define FXAS21002_F_SETUP_F_MODE_CIR_MODE ((uint8_t) 0x40) /* FIFO is in Circular Buffer mode. */ |

Definition at line 307 of file fxas21002.h.

| #define FXAS21002_F_SETUP_F_MODE_FIFO_OFF ((uint8_t) 0x00) /* FIFO is disabled. */ |

Definition at line 306 of file fxas21002.h.

| #define FXAS21002_F_SETUP_F_MODE_MASK ((uint8_t) 0xC0) |

Definition at line 299 of file fxas21002.h.

| #define FXAS21002_F_SETUP_F_MODE_SHIFT ((uint8_t) 6) |

Definition at line 300 of file fxas21002.h.

| #define FXAS21002_F_SETUP_F_MODE_STOP_MODE ((uint8_t) 0x80) /* FIFO is in Stop mode. */ |

Definition at line 308 of file fxas21002.h.

| #define FXAS21002_F_SETUP_F_WMRK_MASK ((uint8_t) 0x3F) |

Definition at line 296 of file fxas21002.h.

| #define FXAS21002_F_SETUP_F_WMRK_SHIFT ((uint8_t) 0) |

Definition at line 297 of file fxas21002.h.

| #define FXAS21002_F_STATUS_F_CNT_MASK ((uint8_t) 0x3F) |

Definition at line 257 of file fxas21002.h.

| #define FXAS21002_F_STATUS_F_CNT_SHIFT ((uint8_t) 0) |

Definition at line 258 of file fxas21002.h.

| #define FXAS21002_F_STATUS_F_OVF_DETECT ((uint8_t) 0x80) /* FIFO Overflow event has been detected. */ |

Definition at line 271 of file fxas21002.h.

| #define FXAS21002_F_STATUS_F_OVF_MASK ((uint8_t) 0x80) |

Definition at line 263 of file fxas21002.h.

| #define FXAS21002_F_STATUS_F_OVF_SHIFT ((uint8_t) 7) |

Definition at line 264 of file fxas21002.h.

| #define FXAS21002_F_STATUS_F_WMKF_DETECT ((uint8_t) 0x40) /* FIFO Watermark event has been detected. */ |

Definition at line 270 of file fxas21002.h.

| #define FXAS21002_F_STATUS_F_WMKF_MASK ((uint8_t) 0x40) |

Definition at line 260 of file fxas21002.h.

| #define FXAS21002_F_STATUS_F_WMKF_SHIFT ((uint8_t) 6) |

Definition at line 261 of file fxas21002.h.

| #define FXAS21002_I2C_ADDRESS 0x20 |

FXAS21002 I2C Address

Definition at line 46 of file fxas21002.h.

| #define FXAS21002_INT_SRC_FLAG_BOOTEND_BOOT_DONE ((uint8_t) 0x08) /* Boot sequence is complete. */ |

Definition at line 395 of file fxas21002.h.

| #define FXAS21002_INT_SRC_FLAG_BOOTEND_MASK ((uint8_t) 0x08) |

Definition at line 382 of file fxas21002.h.

| #define FXAS21002_INT_SRC_FLAG_BOOTEND_SHIFT ((uint8_t) 3) |

Definition at line 383 of file fxas21002.h.

| #define FXAS21002_INT_SRC_FLAG_SRC_DRDY_MASK ((uint8_t) 0x01) |

Definition at line 373 of file fxas21002.h.

| #define FXAS21002_INT_SRC_FLAG_SRC_DRDY_READY ((uint8_t) 0x01) /* Asserted whenever a data-ready event triggers */ |

Definition at line 389 of file fxas21002.h.

| #define FXAS21002_INT_SRC_FLAG_SRC_DRDY_SHIFT ((uint8_t) 0) |

Definition at line 374 of file fxas21002.h.

| #define FXAS21002_INT_SRC_FLAG_SRC_FIFO_EVENT ((uint8_t) 0x04) /* F_OVF or F_WMKF are set, provided the FIFO */ |

Definition at line 393 of file fxas21002.h.

| #define FXAS21002_INT_SRC_FLAG_SRC_FIFO_MASK ((uint8_t) 0x04) |

Definition at line 379 of file fxas21002.h.

| #define FXAS21002_INT_SRC_FLAG_SRC_FIFO_SHIFT ((uint8_t) 2) |

Definition at line 380 of file fxas21002.h.

| #define FXAS21002_INT_SRC_FLAG_SRC_RT_MASK ((uint8_t) 0x02) |

Definition at line 376 of file fxas21002.h.

| #define FXAS21002_INT_SRC_FLAG_SRC_RT_SHIFT ((uint8_t) 1) |

Definition at line 377 of file fxas21002.h.

| #define FXAS21002_INT_SRC_FLAG_SRC_RT_THRESH ((uint8_t) 0x02) /* Indicates that the rate threshold event flag */ |

Definition at line 391 of file fxas21002.h.

| #define FXAS21002_RT_CFG_ELE_DISABLE ((uint8_t) 0x00) /* Event flag latch disabled. */ |

Definition at line 544 of file fxas21002.h.

| #define FXAS21002_RT_CFG_ELE_ENABLE ((uint8_t) 0x08) /* Event flag latch enabled. */ |

Definition at line 543 of file fxas21002.h.

| #define FXAS21002_RT_CFG_ELE_MASK ((uint8_t) 0x08) |

Definition at line 530 of file fxas21002.h.

| #define FXAS21002_RT_CFG_ELE_SHIFT ((uint8_t) 3) |

Definition at line 531 of file fxas21002.h.

| #define FXAS21002_RT_CFG_XTEFE_DISABLE ((uint8_t) 0x00) /* X event detection disabled. */ |

Definition at line 538 of file fxas21002.h.

| #define FXAS21002_RT_CFG_XTEFE_ENABLE ((uint8_t) 0x01) /* X event detection enabled. */ |

Definition at line 537 of file fxas21002.h.

| #define FXAS21002_RT_CFG_XTEFE_MASK ((uint8_t) 0x01) |

Definition at line 521 of file fxas21002.h.

| #define FXAS21002_RT_CFG_XTEFE_SHIFT ((uint8_t) 0) |

Definition at line 522 of file fxas21002.h.

| #define FXAS21002_RT_CFG_YTEFE_DISABLE ((uint8_t) 0x00) /* Y event detection disabled. */ |

Definition at line 540 of file fxas21002.h.

| #define FXAS21002_RT_CFG_YTEFE_ENABLE ((uint8_t) 0x02) /* Y event detection enabled. */ |

Definition at line 539 of file fxas21002.h.

| #define FXAS21002_RT_CFG_YTEFE_MASK ((uint8_t) 0x02) |

Definition at line 524 of file fxas21002.h.

| #define FXAS21002_RT_CFG_YTEFE_SHIFT ((uint8_t) 1) |

Definition at line 525 of file fxas21002.h.

| #define FXAS21002_RT_CFG_ZTEFE_DISABLE ((uint8_t) 0x00) /* Z event detection disabled. */ |

Definition at line 542 of file fxas21002.h.

| #define FXAS21002_RT_CFG_ZTEFE_ENABLE ((uint8_t) 0x04) /* Z event detection enabled. */ |

Definition at line 541 of file fxas21002.h.

| #define FXAS21002_RT_CFG_ZTEFE_MASK ((uint8_t) 0x04) |

Definition at line 527 of file fxas21002.h.

| #define FXAS21002_RT_CFG_ZTEFE_SHIFT ((uint8_t) 2) |

Definition at line 528 of file fxas21002.h.

| #define FXAS21002_RT_SRC_EA_EVENT ((uint8_t) 0x40) /* One or more event flags have been asserted. */ |

Definition at line 617 of file fxas21002.h.

| #define FXAS21002_RT_SRC_EA_MASK ((uint8_t) 0x40) |

Definition at line 597 of file fxas21002.h.

| #define FXAS21002_RT_SRC_EA_NOEVENT ((uint8_t) 0x00) /* No event flags have been asserted. */ |

Definition at line 616 of file fxas21002.h.

| #define FXAS21002_RT_SRC_EA_SHIFT ((uint8_t) 6) |

Definition at line 598 of file fxas21002.h.

| #define FXAS21002_RT_SRC_X_RT_POL_MASK ((uint8_t) 0x01) |

Definition at line 579 of file fxas21002.h.

| #define FXAS21002_RT_SRC_X_RT_POL_NEG ((uint8_t) 0x01) /* Rate Event was Negative. */ |

Definition at line 605 of file fxas21002.h.

| #define FXAS21002_RT_SRC_X_RT_POL_POS ((uint8_t) 0x00) /* Rate Event was Positive. */ |

Definition at line 604 of file fxas21002.h.

| #define FXAS21002_RT_SRC_X_RT_POL_SHIFT ((uint8_t) 0) |

Definition at line 580 of file fxas21002.h.

| #define FXAS21002_RT_SRC_XRT_GREATER ((uint8_t) 0x02) /* Rate greater than RT_THS value. Event has occured. */ |

Definition at line 607 of file fxas21002.h.

| #define FXAS21002_RT_SRC_XRT_LOWER ((uint8_t) 0x00) /* Rate lower than RT_THS value. */ |

Definition at line 606 of file fxas21002.h.

| #define FXAS21002_RT_SRC_XRT_MASK ((uint8_t) 0x02) |

Definition at line 582 of file fxas21002.h.

| #define FXAS21002_RT_SRC_XRT_SHIFT ((uint8_t) 1) |

Definition at line 583 of file fxas21002.h.

| #define FXAS21002_RT_SRC_Y_RT_POL_MASK ((uint8_t) 0x04) |

Definition at line 585 of file fxas21002.h.

| #define FXAS21002_RT_SRC_Y_RT_POL_NEG ((uint8_t) 0x04) /* Rate Event was Negative. */ |

Definition at line 609 of file fxas21002.h.

| #define FXAS21002_RT_SRC_Y_RT_POL_POS ((uint8_t) 0x00) /* Rate Event was Positive. */ |

Definition at line 608 of file fxas21002.h.

| #define FXAS21002_RT_SRC_Y_RT_POL_SHIFT ((uint8_t) 2) |

Definition at line 586 of file fxas21002.h.

| #define FXAS21002_RT_SRC_YRT_GREATER ((uint8_t) 0x08) /* Rate greater than RT_THS value. Event has occured. */ |

Definition at line 611 of file fxas21002.h.

| #define FXAS21002_RT_SRC_YRT_LOWER ((uint8_t) 0x00) /* Rate lower than RT_THS value. */ |

Definition at line 610 of file fxas21002.h.

| #define FXAS21002_RT_SRC_YRT_MASK ((uint8_t) 0x08) |

Definition at line 588 of file fxas21002.h.

| #define FXAS21002_RT_SRC_YRT_SHIFT ((uint8_t) 3) |

Definition at line 589 of file fxas21002.h.

| #define FXAS21002_RT_SRC_Z_RT_POL_MASK ((uint8_t) 0x10) |

Definition at line 591 of file fxas21002.h.

| #define FXAS21002_RT_SRC_Z_RT_POL_NEG ((uint8_t) 0x10) /* Rate Event was Negative. */ |

Definition at line 613 of file fxas21002.h.

| #define FXAS21002_RT_SRC_Z_RT_POL_POS ((uint8_t) 0x00) /* Rate Event was Positive. */ |

Definition at line 612 of file fxas21002.h.

| #define FXAS21002_RT_SRC_Z_RT_POL_SHIFT ((uint8_t) 4) |

Definition at line 592 of file fxas21002.h.

| #define FXAS21002_RT_SRC_ZRT_GREATER ((uint8_t) 0x20) /* Rate greater than RT_THS value. Event has occured. */ |

Definition at line 615 of file fxas21002.h.

| #define FXAS21002_RT_SRC_ZRT_LOWER ((uint8_t) 0x00) /* Rate lower than RT_THS value. */ |

Definition at line 614 of file fxas21002.h.

| #define FXAS21002_RT_SRC_ZRT_MASK ((uint8_t) 0x20) |

Definition at line 594 of file fxas21002.h.

| #define FXAS21002_RT_SRC_ZRT_SHIFT ((uint8_t) 5) |

Definition at line 595 of file fxas21002.h.

| #define FXAS21002_RT_THS_DBCNTM_CLEAR ((uint8_t) 0x80) /* Clear counter when angular rate is below the */ |

Definition at line 655 of file fxas21002.h.

| #define FXAS21002_RT_THS_DBCNTM_DECREMENT ((uint8_t) 0x00) /* Decrement counter on every ODR cycle that the */ |

Definition at line 657 of file fxas21002.h.

| #define FXAS21002_RT_THS_DBCNTM_MASK ((uint8_t) 0x80) |

Definition at line 648 of file fxas21002.h.

| #define FXAS21002_RT_THS_DBCNTM_SHIFT ((uint8_t) 7) |

Definition at line 649 of file fxas21002.h.

| #define FXAS21002_RT_THS_THS_MASK ((uint8_t) 0x7F) |

Definition at line 645 of file fxas21002.h.

| #define FXAS21002_RT_THS_THS_SHIFT ((uint8_t) 0) |

Definition at line 646 of file fxas21002.h.

| #define FXAS21002_WHO_AM_I_WHOAMI_MASK ((uint8_t) 0xFF) |

Definition at line 419 of file fxas21002.h.

| #define FXAS21002_WHO_AM_I_WHOAMI_OLD_VALUE ((uint8_t) 0xd1) /* FXAS21000 */ |

Definition at line 426 of file fxas21002.h.

| #define FXAS21002_WHO_AM_I_WHOAMI_PRE_VALUE ((uint8_t) 0xd6) /* Engineering Samples */ |

Definition at line 427 of file fxas21002.h.

| #define FXAS21002_WHO_AM_I_WHOAMI_PROD_VALUE ((uint8_t) 0xd7) /* FXAS21002 Rev 2.1 (production) */ |

Definition at line 428 of file fxas21002.h.

Referenced by main().

| #define FXAS21002_WHO_AM_I_WHOAMI_SHIFT ((uint8_t) 0) |

Definition at line 420 of file fxas21002.h.

| typedef uint8_t FXAS21002_OUT_X_LSB_t |

Definition at line 103 of file fxas21002.h.

| typedef uint8_t FXAS21002_OUT_X_MSB_t |

Definition at line 94 of file fxas21002.h.

| typedef uint8_t FXAS21002_OUT_Y_LSB_t |

Definition at line 122 of file fxas21002.h.

| typedef uint8_t FXAS21002_OUT_Y_MSB_t |

Definition at line 113 of file fxas21002.h.

| typedef uint8_t FXAS21002_OUT_Z_LSB_t |

Definition at line 141 of file fxas21002.h.

| typedef uint8_t FXAS21002_OUT_Z_MSB_t |

Definition at line 132 of file fxas21002.h.

| typedef uint8_t FXAS21002_RT_COUNT_t |

Definition at line 669 of file fxas21002.h.

| typedef uint8_t FXAS21002_STATUS_t |

Definition at line 84 of file fxas21002.h.

| typedef uint8_t FXAS21002_TEMP_t |

Definition at line 679 of file fxas21002.h.

| anonymous enum |

The FXAS21002 Sensor Register Map.

Definition at line 52 of file fxas21002.h.