|

ISSDK

1.7

IoT Sensing Software Development Kit

|

|

ISSDK

1.7

IoT Sensing Software Development Kit

|

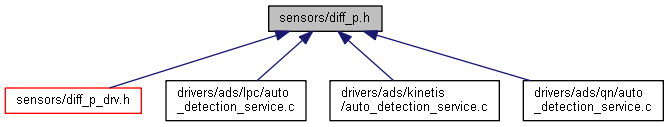

The diff_p.h contains the DIFF_P Pressure sensor register definitions, access macros, and its bit mask. More...

Go to the source code of this file.

Data Structures | |

| union | DIFF_P_INT_STATUS_0_t |

| union | DIFF_P_INT_STATUS_1_t |

| union | DIFF_P_INT_MASK0_t |

| union | DIFF_P_INT_MASK1_t |

| union | DIFF_P_STATUS_t |

| union | DIFF_P_CTRL_REG1_t |

| union | DIFF_P_CTRL_REG2_t |

| union | DIFF_P_CTRL_REG3_t |

| union | DIFF_P_INT_ROUTE0_t |

| union | DIFF_P_INT_ROUTE1_t |

Macros | |

| #define | DIFF_P_NPS3000VV_WHOAMI_VALUE (0xD0) /* DIFF_P Who_Am_I Value of Part Number NPS3000VV. */ |

| #define | DIFF_P_NPS3001DV_WHOAMI_VALUE (0xD1) /* DIFF_P Who_Am_I Value of Part Number NPS3001DV. */ |

| #define | DIFF_P_NPS3002VV_WHOAMI_VALUE (0xD2) /* DIFF_P Who_Am_I Value of Part Number NPS3000VV. */ |

| #define | DIFF_P_NPS3005DV_WHOAMI_VALUE (0xD3) /* DIFF_P Who_Am_I Value of Part Number NPS3000VV. */ |

| #define | DIFF_P_INT_STATUS_0_PDU_MASK ((uint8_t) 0x01) |

| #define | DIFF_P_INT_STATUS_0_PDU_SHIFT ((uint8_t) 0) |

| #define | DIFF_P_INT_STATUS_0_PDO_MASK ((uint8_t) 0x02) |

| #define | DIFF_P_INT_STATUS_0_PDO_SHIFT ((uint8_t) 1) |

| #define | DIFF_P_INT_STATUS_0_VERRA_MASK ((uint8_t) 0x08) |

| #define | DIFF_P_INT_STATUS_0_VERRA_SHIFT ((uint8_t) 3) |

| #define | DIFF_P_INT_STATUS_0_TDR_MASK ((uint8_t) 0x10) |

| #define | DIFF_P_INT_STATUS_0_TDR_SHIFT ((uint8_t) 4) |

| #define | DIFF_P_INT_STATUS_0_PDR_MASK ((uint8_t) 0x20) |

| #define | DIFF_P_INT_STATUS_0_PDR_SHIFT ((uint8_t) 5) |

| #define | DIFF_P_INT_STATUS_0_TOW_MASK ((uint8_t) 0x40) |

| #define | DIFF_P_INT_STATUS_0_TOW_SHIFT ((uint8_t) 6) |

| #define | DIFF_P_INT_STATUS_0_POW_MASK ((uint8_t) 0x80) |

| #define | DIFF_P_INT_STATUS_0_POW_SHIFT ((uint8_t) 7) |

| #define | DIFF_P_INT_STATUS_0_PDU_UNDERFLOW ((uint8_t) 0x01) /* Underflow occurred. */ |

| #define | DIFF_P_INT_STATUS_0_PDU_NO_UNDERFLOW ((uint8_t) 0x00) /* No Underflow occurred. */ |

| #define | DIFF_P_INT_STATUS_0_PDO_OVERFLOW ((uint8_t) 0x02) /* Overflow occurred. */ |

| #define | DIFF_P_INT_STATUS_0_PDO_NO_OVERFLOW ((uint8_t) 0x00) /* No overflow occurred. */ |

| #define | DIFF_P_INT_STATUS_0_VERRA_BRWNOUT ((uint8_t) 0x08) /* Analog voltage brownout occurred. */ |

| #define | DIFF_P_INT_STATUS_0_VERRA_NO_BRWNOUT ((uint8_t) 0x00) /* No brownout occurred. */ |

| #define | DIFF_P_INT_STATUS_0_TDR_DRDY ((uint8_t) 0x10) /* A new Temperature data is ready. */ |

| #define | DIFF_P_INT_STATUS_0_PDR_DRDY ((uint8_t) 0x20) /* A new set of Pressure data is ready. */ |

| #define | DIFF_P_INT_STATUS_0_TOW_OWR ((uint8_t) 0x40) /* Previous Temperature data was overwritten by new */ |

| #define | DIFF_P_INT_STATUS_0_POW_OWR ((uint8_t) 0x80) /* Previous Pressure data was overwritten by new */ |

| #define | DIFF_P_INT_STATUS_1_P_WCHG_MASK ((uint8_t) 0x02) |

| #define | DIFF_P_INT_STATUS_1_P_WCHG_SHIFT ((uint8_t) 1) |

| #define | DIFF_P_INT_STATUS_1_P_TGT2_MASK ((uint8_t) 0x04) |

| #define | DIFF_P_INT_STATUS_1_P_TGT2_SHIFT ((uint8_t) 2) |

| #define | DIFF_P_INT_STATUS_1_P_TGT1_MASK ((uint8_t) 0x08) |

| #define | DIFF_P_INT_STATUS_1_P_TGT1_SHIFT ((uint8_t) 3) |

| #define | DIFF_P_INT_STATUS_1_P_TGT0_MASK ((uint8_t) 0x10) |

| #define | DIFF_P_INT_STATUS_1_P_TGT0_SHIFT ((uint8_t) 4) |

| #define | DIFF_P_INT_STATUS_1_T_TGT_MASK ((uint8_t) 0x20) |

| #define | DIFF_P_INT_STATUS_1_T_TGT_SHIFT ((uint8_t) 5) |

| #define | DIFF_P_INT_STATUS_1_TDU_MASK ((uint8_t) 0x40) |

| #define | DIFF_P_INT_STATUS_1_TDU_SHIFT ((uint8_t) 6) |

| #define | DIFF_P_INT_STATUS_1_TDO_MASK ((uint8_t) 0x80) |

| #define | DIFF_P_INT_STATUS_1_TDO_SHIFT ((uint8_t) 7) |

| #define | DIFF_P_INT_STATUS_1_P_WCHG_TH_CROSSED ((uint8_t) 0x02) /* pressure has crossed the window threshold defined */ |

| #define | DIFF_P_INT_STATUS_1_P_TGT2_REACHED ((uint8_t) 0x04) /* Temperature target reached. */ |

| #define | DIFF_P_INT_STATUS_1_P_TGT1_REACHED ((uint8_t) 0x08) /* Temperature target reached. */ |

| #define | DIFF_P_INT_STATUS_1_P_TGT0_REACHED ((uint8_t) 0x10) /* Temperature target reached. */ |

| #define | DIFF_P_INT_STATUS_1_T_TGT_REACHED ((uint8_t) 0x20) /* Temperature target reached. */ |

| #define | DIFF_P_INT_STATUS_1_TDU_UNDERFLOW ((uint8_t) 0x40) /* Underflow occurred. */ |

| #define | DIFF_P_INT_STATUS_1_TDU_NO_UNDERFLOW ((uint8_t) 0x00) /* No Underflow occurred. */ |

| #define | DIFF_P_INT_STATUS_1_TDO_OVERFLOW ((uint8_t) 0x80) /* Overflow occurred. */ |

| #define | DIFF_P_INT_STATUS_1_TDO_NO_OVERFLOW ((uint8_t) 0x00) /* No overflow occurred. */ |

| #define | DIFF_P_INT_MASK0_PDU_MASK ((uint8_t) 0x01) |

| #define | DIFF_P_INT_MASK0_PDU_SHIFT ((uint8_t) 0) |

| #define | DIFF_P_INT_MASK0_PDO_MASK ((uint8_t) 0x02) |

| #define | DIFF_P_INT_MASK0_PDO_SHIFT ((uint8_t) 1) |

| #define | DIFF_P_INT_MASK0_VERRA_MASK ((uint8_t) 0x08) |

| #define | DIFF_P_INT_MASK0_VERRA_SHIFT ((uint8_t) 3) |

| #define | DIFF_P_INT_MASK0_TDR_MASK ((uint8_t) 0x10) |

| #define | DIFF_P_INT_MASK0_TDR_SHIFT ((uint8_t) 4) |

| #define | DIFF_P_INT_MASK0_PDR_MASK ((uint8_t) 0x20) |

| #define | DIFF_P_INT_MASK0_PDR_SHIFT ((uint8_t) 5) |

| #define | DIFF_P_INT_MASK0_TOW_MASK ((uint8_t) 0x40) |

| #define | DIFF_P_INT_MASK0_TOW_SHIFT ((uint8_t) 6) |

| #define | DIFF_P_INT_MASK0_POW_MASK ((uint8_t) 0x80) |

| #define | DIFF_P_INT_MASK0_POW_SHIFT ((uint8_t) 7) |

| #define | DIFF_P_INT_MASK0_PDU_INT_EN ((uint8_t) 0x01) /* Interrupt Enabled. */ |

| #define | DIFF_P_INT_MASK0_PDO_INT_EN ((uint8_t) 0x02) /* Interrupt Enabled. */ |

| #define | DIFF_P_INT_MASK0_VERRA_INT_EN ((uint8_t) 0x08) /* Interrupt Enabled. */ |

| #define | DIFF_P_INT_MASK0_TDR_INT_EN ((uint8_t) 0x10) /* Interrupt Enabled. */ |

| #define | DIFF_P_INT_MASK0_PDR_INT_EN ((uint8_t) 0x20) /* Interrupt Enabled. */ |

| #define | DIFF_P_INT_MASK0_TOW_INT_EN ((uint8_t) 0x40) /* Interrupt Enabled. */ |

| #define | DIFF_P_INT_MASK0_POW_INT_EN ((uint8_t) 0x80) /* Interrupt Enabled. */ |

| #define | DIFF_P_INT_MASK1_P_WCHG_MASK ((uint8_t) 0x02) |

| #define | DIFF_P_INT_MASK1_P_WCHG_SHIFT ((uint8_t) 1) |

| #define | DIFF_P_INT_MASK1_P_TGT2_MASK ((uint8_t) 0x04) |

| #define | DIFF_P_INT_MASK1_P_TGT2_SHIFT ((uint8_t) 2) |

| #define | DIFF_P_INT_MASK1_P_TGT1_MASK ((uint8_t) 0x08) |

| #define | DIFF_P_INT_MASK1_P_TGT1_SHIFT ((uint8_t) 3) |

| #define | DIFF_P_INT_MASK1_P_TGT0_MASK ((uint8_t) 0x10) |

| #define | DIFF_P_INT_MASK1_P_TGT0_SHIFT ((uint8_t) 4) |

| #define | DIFF_P_INT_MASK1_T_TGT_MASK ((uint8_t) 0x20) |

| #define | DIFF_P_INT_MASK1_T_TGT_SHIFT ((uint8_t) 5) |

| #define | DIFF_P_INT_MASK1_TDU_MASK ((uint8_t) 0x40) |

| #define | DIFF_P_INT_MASK1_TDU_SHIFT ((uint8_t) 6) |

| #define | DIFF_P_INT_MASK1_TDO_MASK ((uint8_t) 0x80) |

| #define | DIFF_P_INT_MASK1_TDO_SHIFT ((uint8_t) 7) |

| #define | DIFF_P_INT_MASK1_P_WCHG_INT_EN ((uint8_t) 0x02) /* Interrupt Enabled. */ |

| #define | DIFF_P_INT_MASK1_P_TGT2_INT_EN ((uint8_t) 0x04) /* Interrupt Enabled. */ |

| #define | DIFF_P_INT_MASK1_P_TGT1_INT_EN ((uint8_t) 0x08) /* Interrupt Enabled. */ |

| #define | DIFF_P_INT_MASK1_P_TGT0_INT_EN ((uint8_t) 0x10) /* Interrupt Enabled. */ |

| #define | DIFF_P_INT_MASK1_T_TGT_INT_EN ((uint8_t) 0x20) /* Interrupt Enabled. */ |

| #define | DIFF_P_INT_MASK1_TDU_INT_EN ((uint8_t) 0x40) /* Interrupt Enabled. */ |

| #define | DIFF_P_INT_MASK1_TDO_INT_EN ((uint8_t) 0x80) /* Interrupt Enabled. */ |

| #define | DIFF_P_STATUS_RST_STATUS_MASK ((uint8_t) 0x01) |

| #define | DIFF_P_STATUS_RST_STATUS_SHIFT ((uint8_t) 0) |

| #define | DIFF_P_STATUS_OSR_ERR_MASK ((uint8_t) 0x02) |

| #define | DIFF_P_STATUS_OSR_ERR_SHIFT ((uint8_t) 1) |

| #define | DIFF_P_STATUS_STAT_CPLT_MASK ((uint8_t) 0x04) |

| #define | DIFF_P_STATUS_STAT_CPLT_SHIFT ((uint8_t) 2) |

| #define | DIFF_P_STATUS_STAT_EP_MASK ((uint8_t) 0x08) |

| #define | DIFF_P_STATUS_STAT_EP_SHIFT ((uint8_t) 3) |

| #define | DIFF_P_STATUS_I2C_RPG_STATUS_MASK ((uint8_t) 0x10) |

| #define | DIFF_P_STATUS_I2C_RPG_STATUS_SHIFT ((uint8_t) 4) |

| #define | DIFF_P_STATUS_I2C_RPG_MASK ((uint8_t) 0x20) |

| #define | DIFF_P_STATUS_I2C_RPG_SHIFT ((uint8_t) 5) |

| #define | DIFF_P_STATUS_I2C_RPG_CNT_MASK ((uint8_t) 0x40) |

| #define | DIFF_P_STATUS_I2C_RPG_CNT_SHIFT ((uint8_t) 6) |

| #define | DIFF_P_STATUS_ACTIVE_MODE_MASK ((uint8_t) 0x80) |

| #define | DIFF_P_STATUS_ACTIVE_MODE_SHIFT ((uint8_t) 7) |

| #define | DIFF_P_STATUS_RST_STATUS_RST ((uint8_t) 0x01) /* Part has come out of POR, brownout or soft reset. */ |

| #define | DIFF_P_STATUS_RST_STATUS_NO_RST ((uint8_t) 0x00) /* No POR, brownout or soft reset has occurred. */ |

| #define | DIFF_P_STATUS_OSR_ERR_ERR ((uint8_t) 0x02) /* Illegal ODR/OSR combination. */ |

| #define | DIFF_P_STATUS_OSR_ERR_NO_ERR ((uint8_t) 0x00) /* No Error. */ |

| #define | DIFF_P_STATUS_STAT_CPLT_SUCCESS ((uint8_t) 0x04) /* Calibration routine was successful. */ |

| #define | DIFF_P_STATUS_STAT_CPLT_NO_SUCCESS ((uint8_t) 0x00) /* Calibration routine was not successful. */ |

| #define | DIFF_P_STATUS_STAT_EP_DETECTED ((uint8_t) 0x08) /* Existing pressure has been detected. */ |

| #define | DIFF_P_STATUS_STAT_EP_NOTDETECTED ((uint8_t) 0x00) /* No existing pressure detected. */ |

| #define | DIFF_P_STATUS_I2C_RPG_STATUS_RPG_INIT ((uint8_t) 0x10) /* Reprograming cycle initiated. */ |

| #define | DIFF_P_STATUS_I2C_RPG_STATUS_RPG_CPLT ((uint8_t) 0x00) /* Reprograming cycle completed. */ |

| #define | DIFF_P_STATUS_I2C_RPG_RPG_SUCCESS ((uint8_t) 0x20) /* I2C Reprograming successful. */ |

| #define | DIFF_P_STATUS_I2C_RPG_NO_RPG ((uint8_t) 0x00) /* No Reprograming has taken place. */ |

| #define | DIFF_P_STATUS_I2C_RPG_CNT_CANT_RPG ((uint8_t) 0x40) /* I2C address cannot be reprogrammed. */ |

| #define | DIFF_P_STATUS_I2C_RPG_CNT_CAN_RPG ((uint8_t) 0x00) /* I2C address can be reprogrammed. */ |

| #define | DIFF_P_STATUS_ACTIVE_MODE_ACTIVE ((uint8_t) 0x80) /* Sensor is in active mode. */ |

| #define | DIFF_P_STATUS_ACTIVE_MODE_STANDBY ((uint8_t) 0x00) /* Sensor is in standby mode. */ |

| #define | DIFF_P_CTRL_REG1_SBYB_MASK ((uint8_t) 0x01) |

| #define | DIFF_P_CTRL_REG1_SBYB_SHIFT ((uint8_t) 0) |

| #define | DIFF_P_CTRL_REG1_OST_MASK ((uint8_t) 0x02) |

| #define | DIFF_P_CTRL_REG1_OST_SHIFT ((uint8_t) 1) |

| #define | DIFF_P_CTRL_REG1_RST_MASK ((uint8_t) 0x04) |

| #define | DIFF_P_CTRL_REG1_RST_SHIFT ((uint8_t) 2) |

| #define | DIFF_P_CTRL_REG1_OSR_MASK ((uint8_t) 0xF8) |

| #define | DIFF_P_CTRL_REG1_OSR_SHIFT ((uint8_t) 3) |

| #define | DIFF_P_CTRL_REG1_SBYB_ACTIVE ((uint8_t) 0x01) /* Part is ACTIVE. */ |

| #define | DIFF_P_CTRL_REG1_SBYB_STANDBY ((uint8_t) 0x00) /* Part is in STANDBY mode. */ |

| #define | DIFF_P_CTRL_REG1_OST_ONESHOT ((uint8_t) 0x02) /* One Shot Mode. */ |

| #define | DIFF_P_CTRL_REG1_OST_NORMAL ((uint8_t) 0x00) /* Normal operating mode. */ |

| #define | DIFF_P_CTRL_REG1_RST_RESET ((uint8_t) 0x04) /* Device will be reset. */ |

| #define | DIFF_P_CTRL_REG1_RST_NORMAL ((uint8_t) 0x00) /* Normal operating mode. */ |

| #define | DIFF_P_CTRL_REG1_OSR_OSR1 ((uint8_t) 0x00) /* Oversampling Rate#1. */ |

| #define | DIFF_P_CTRL_REG1_OSR_OSR2 ((uint8_t) 0x08) /* Oversampling Rate#2. */ |

| #define | DIFF_P_CTRL_REG1_OSR_OSR4 ((uint8_t) 0x10) /* Oversampling Rate#4. */ |

| #define | DIFF_P_CTRL_REG1_OSR_OSR8 ((uint8_t) 0x18) /* Oversampling Rate#8. */ |

| #define | DIFF_P_CTRL_REG1_OSR_OSR16 ((uint8_t) 0x20) /* Oversampling Rate#16. */ |

| #define | DIFF_P_CTRL_REG1_OSR_OSR32 ((uint8_t) 0x28) /* Oversampling Rate#32. */ |

| #define | DIFF_P_CTRL_REG1_OSR_OSR64 ((uint8_t) 0x30) /* Oversampling Rate#64. */ |

| #define | DIFF_P_CTRL_REG1_OSR_OSR128 ((uint8_t) 0x38) /* Oversampling Rate#128. */ |

| #define | DIFF_P_CTRL_REG1_OSR_OSR256 ((uint8_t) 0x40) /* Oversampling Rate#256. */ |

| #define | DIFF_P_CTRL_REG1_OSR_OSR512 ((uint8_t) 0x48) /* Oversampling Rate#512. */ |

| #define | DIFF_P_CTRL_REG1_OSR_OSR768 ((uint8_t) 0x50) /* Oversampling Rate#768. */ |

| #define | DIFF_P_CTRL_REG1_OSR_OSR1024 ((uint8_t) 0x58) /* Oversampling Rate#1024. */ |

| #define | DIFF_P_CTRL_REG1_OSR_OSR1280 ((uint8_t) 0x60) /* Oversampling Rate#1280. */ |

| #define | DIFF_P_CTRL_REG1_OSR_OSR1536 ((uint8_t) 0x68) /* Oversampling Rate#1536. */ |

| #define | DIFF_P_CTRL_REG1_OSR_OSR2048 ((uint8_t) 0x70) /* Oversampling Rate#2048. */ |

| #define | DIFF_P_CTRL_REG1_OSR_OSR2560 ((uint8_t) 0x78) /* Oversampling Rate#2560. */ |

| #define | DIFF_P_CTRL_REG1_OSR_OSR3072 ((uint8_t) 0x80) /* Oversampling Rate#3072. */ |

| #define | DIFF_P_CTRL_REG1_OSR_OSR4096 ((uint8_t) 0x88) /* Oversampling Rate#4096. */ |

| #define | DIFF_P_CTRL_REG1_OSR_OSR5120 ((uint8_t) 0x90) /* Oversampling Rate#5120. */ |

| #define | DIFF_P_CTRL_REG1_OSR_OSR6144 ((uint8_t) 0x98) /* Oversampling Rate#6144. */ |

| #define | DIFF_P_CTRL_REG1_OSR_OSR7168 ((uint8_t) 0xa0) /* Oversampling Rate#7168. */ |

| #define | DIFF_P_CTRL_REG1_OSR_OSR8192 ((uint8_t) 0xa8) /* Oversampling Rate#8192. */ |

| #define | DIFF_P_CTRL_REG2_ODR_MASK ((uint8_t) 0x0F) |

| #define | DIFF_P_CTRL_REG2_ODR_SHIFT ((uint8_t) 0) |

| #define | DIFF_P_CTRL_REG2_F_READ_MASK ((uint8_t) 0x20) |

| #define | DIFF_P_CTRL_REG2_F_READ_SHIFT ((uint8_t) 5) |

| #define | DIFF_P_CTRL_REG2_BRWNOUT_EN_MASK ((uint8_t) 0x40) |

| #define | DIFF_P_CTRL_REG2_BRWNOUT_EN_SHIFT ((uint8_t) 6) |

| #define | DIFF_P_CTRL_REG2_CTRL_AC_MASK ((uint8_t) 0x80) |

| #define | DIFF_P_CTRL_REG2_CTRL_AC_SHIFT ((uint8_t) 7) |

| #define | DIFF_P_CTRL_REG2_ODR_ODR3200 ((uint8_t) 0x00) /* Output Data Rate#3200. */ |

| #define | DIFF_P_CTRL_REG2_ODR_ODR1600 ((uint8_t) 0x01) /* Output Data Rate#1600. */ |

| #define | DIFF_P_CTRL_REG2_ODR_ODR800 ((uint8_t) 0x02) /* Output Data Rate#800. */ |

| #define | DIFF_P_CTRL_REG2_ODR_ODR400 ((uint8_t) 0x03) /* Output Data Rate#400. */ |

| #define | DIFF_P_CTRL_REG2_ODR_ODR200 ((uint8_t) 0x04) /* Output Data Rate#200. */ |

| #define | DIFF_P_CTRL_REG2_ODR_ODR100 ((uint8_t) 0x05) /* Output Data Rate#100. */ |

| #define | DIFF_P_CTRL_REG2_ODR_ODR50 ((uint8_t) 0x06) /* Output Data Rate#50. */ |

| #define | DIFF_P_CTRL_REG2_ODR_ODR25 ((uint8_t) 0x07) /* Output Data Rate#25. */ |

| #define | DIFF_P_CTRL_REG2_ODR_ODR12P5 ((uint8_t) 0x08) /* Output Data Rate#12.5. */ |

| #define | DIFF_P_CTRL_REG2_ODR_ODR6P25 ((uint8_t) 0x09) /* Output Data Rate#6.25. */ |

| #define | DIFF_P_CTRL_REG2_ODR_ODR3P125 ((uint8_t) 0x0a) /* Output Data Rate#3.125. */ |

| #define | DIFF_P_CTRL_REG2_ODR_ODR1P563 ((uint8_t) 0x0b) /* Output Data Rate#1.563. */ |

| #define | DIFF_P_CTRL_REG2_ODR_ODR0P781 ((uint8_t) 0x0c) /* Output Data Rate#0.781. */ |

| #define | DIFF_P_CTRL_REG2_F_READ_NORMAL ((uint8_t) 0x20) /* Loops between all register addresses. */ |

| #define | DIFF_P_CTRL_REG2_F_READ_FASTREAD ((uint8_t) 0x00) /* Loops between register address 0x00 and 0x04. */ |

| #define | DIFF_P_CTRL_REG2_BRWNOUT_EN_ENABLED ((uint8_t) 0x40) /* Internal brown out circuit is enabled. */ |

| #define | DIFF_P_CTRL_REG2_BRWNOUT_EN_DISABLED ((uint8_t) 0x00) /* Internal brown out circuit is disabled. */ |

| #define | DIFF_P_CTRL_REG2_CTRL_AC_CALRUN ((uint8_t) 0x80) /* Run Calibration Algorithm. */ |

| #define | DIFF_P_CTRL_REG2_CTRL_AC_NOCALRUN ((uint8_t) 0x00) /* Calibration Algorithm not run. */ |

| #define | DIFF_P_CTRL_REG3_PP_OD2_MASK ((uint8_t) 0x01) |

| #define | DIFF_P_CTRL_REG3_PP_OD2_SHIFT ((uint8_t) 0) |

| #define | DIFF_P_CTRL_REG3_IPOL2_MASK ((uint8_t) 0x02) |

| #define | DIFF_P_CTRL_REG3_IPOL2_SHIFT ((uint8_t) 1) |

| #define | DIFF_P_CTRL_REG3_PP_OD1_MASK ((uint8_t) 0x10) |

| #define | DIFF_P_CTRL_REG3_PP_OD1_SHIFT ((uint8_t) 4) |

| #define | DIFF_P_CTRL_REG3_IPOL1_MASK ((uint8_t) 0x20) |

| #define | DIFF_P_CTRL_REG3_IPOL1_SHIFT ((uint8_t) 5) |

| #define | DIFF_P_CTRL_REG3_PP_OD2_OPENDRAIN ((uint8_t) 0x01) /* Open drain. */ |

| #define | DIFF_P_CTRL_REG3_PP_OD2_PUSHPULL ((uint8_t) 0x00) /* Push-pull. */ |

| #define | DIFF_P_CTRL_REG3_IPOL2_ACTIVE_HIGH ((uint8_t) 0x02) /* Active High. */ |

| #define | DIFF_P_CTRL_REG3_IPOL2_ACTIVE_LOW ((uint8_t) 0x00) /* Active Low. */ |

| #define | DIFF_P_CTRL_REG3_PP_OD1_OPENDRAIN ((uint8_t) 0x10) /* Open drain. */ |

| #define | DIFF_P_CTRL_REG3_PP_OD1_PUSHPULL ((uint8_t) 0x00) /* Push-pull. */ |

| #define | DIFF_P_CTRL_REG3_IPOL1_ACTIVE_HIGH ((uint8_t) 0x20) /* Active High. */ |

| #define | DIFF_P_CTRL_REG3_IPOL1_ACTIVE_LOW ((uint8_t) 0x00) /* Active Low. */ |

| #define | DIFF_P_INT_ROUTE0_PDU_MASK ((uint8_t) 0x01) |

| #define | DIFF_P_INT_ROUTE0_PDU_SHIFT ((uint8_t) 0) |

| #define | DIFF_P_INT_ROUTE0_PDO_MASK ((uint8_t) 0x02) |

| #define | DIFF_P_INT_ROUTE0_PDO_SHIFT ((uint8_t) 1) |

| #define | DIFF_P_INT_ROUTE0_VERRA_MASK ((uint8_t) 0x08) |

| #define | DIFF_P_INT_ROUTE0_VERRA_SHIFT ((uint8_t) 3) |

| #define | DIFF_P_INT_ROUTE0_TDR_MASK ((uint8_t) 0x10) |

| #define | DIFF_P_INT_ROUTE0_TDR_SHIFT ((uint8_t) 4) |

| #define | DIFF_P_INT_ROUTE0_PDR_MASK ((uint8_t) 0x20) |

| #define | DIFF_P_INT_ROUTE0_PDR_SHIFT ((uint8_t) 5) |

| #define | DIFF_P_INT_ROUTE0_TOW_MASK ((uint8_t) 0x40) |

| #define | DIFF_P_INT_ROUTE0_TOW_SHIFT ((uint8_t) 6) |

| #define | DIFF_P_INT_ROUTE0_POW_MASK ((uint8_t) 0x80) |

| #define | DIFF_P_INT_ROUTE0_POW_SHIFT ((uint8_t) 7) |

| #define | DIFF_P_INT_ROUTE0_PDU_INT2 ((uint8_t) 0x01) /* Interrupt routed to INT2 pin. */ |

| #define | DIFF_P_INT_ROUTE0_PDU_INT1 ((uint8_t) 0x00) /* Interrupt routed to INT1 pin. */ |

| #define | DIFF_P_INT_ROUTE0_PDO_INT2 ((uint8_t) 0x02) /* Interrupt routed to INT2 pin. */ |

| #define | DIFF_P_INT_ROUTE0_PDO_INT1 ((uint8_t) 0x00) /* Interrupt routed to INT1 pin. */ |

| #define | DIFF_P_INT_ROUTE0_VERRA_INT2 ((uint8_t) 0x08) /* Interrupt routed to INT2 pin. */ |

| #define | DIFF_P_INT_ROUTE0_VERRA_INT1 ((uint8_t) 0x00) /* Interrupt routed to INT1 pin. */ |

| #define | DIFF_P_INT_ROUTE0_TDR_INT2 ((uint8_t) 0x10) /* Interrupt routed to INT2 pin. */ |

| #define | DIFF_P_INT_ROUTE0_TDR_INT1 ((uint8_t) 0x00) /* Interrupt routed to INT1 pin. */ |

| #define | DIFF_P_INT_ROUTE0_PDR_INT2 ((uint8_t) 0x20) /* Interrupt routed to INT2 pin. */ |

| #define | DIFF_P_INT_ROUTE0_PDR_INT1 ((uint8_t) 0x00) /* Interrupt routed to INT1 pin. */ |

| #define | DIFF_P_INT_ROUTE0_TOW_INT2 ((uint8_t) 0x40) /* Interrupt routed to INT2 pin. */ |

| #define | DIFF_P_INT_ROUTE0_TOW_INT1 ((uint8_t) 0x00) /* Interrupt routed to INT1 pin. */ |

| #define | DIFF_P_INT_ROUTE0_POW_INT2 ((uint8_t) 0x80) /* Interrupt routed to INT2 pin. */ |

| #define | DIFF_P_INT_ROUTE0_POW_INT1 ((uint8_t) 0x00) /* Interrupt routed to INT1 pin. */ |

| #define | DIFF_P_INT_ROUTE1_P_WCHG_MASK ((uint8_t) 0x02) |

| #define | DIFF_P_INT_ROUTE1_P_WCHG_SHIFT ((uint8_t) 1) |

| #define | DIFF_P_INT_ROUTE1_P_TGT2_MASK ((uint8_t) 0x04) |

| #define | DIFF_P_INT_ROUTE1_P_TGT2_SHIFT ((uint8_t) 2) |

| #define | DIFF_P_INT_ROUTE1_P_TGT1_MASK ((uint8_t) 0x08) |

| #define | DIFF_P_INT_ROUTE1_P_TGT1_SHIFT ((uint8_t) 3) |

| #define | DIFF_P_INT_ROUTE1_P_TGT0_MASK ((uint8_t) 0x10) |

| #define | DIFF_P_INT_ROUTE1_P_TGT0_SHIFT ((uint8_t) 4) |

| #define | DIFF_P_INT_ROUTE1_T_TGT_MASK ((uint8_t) 0x20) |

| #define | DIFF_P_INT_ROUTE1_T_TGT_SHIFT ((uint8_t) 5) |

| #define | DIFF_P_INT_ROUTE1_TDU_MASK ((uint8_t) 0x40) |

| #define | DIFF_P_INT_ROUTE1_TDU_SHIFT ((uint8_t) 6) |

| #define | DIFF_P_INT_ROUTE1_TDO_MASK ((uint8_t) 0x80) |

| #define | DIFF_P_INT_ROUTE1_TDO_SHIFT ((uint8_t) 7) |

| #define | DIFF_P_INT_ROUTE1_P_WCHG_INT2 ((uint8_t) 0x02) /* Interrupt routed to INT2 pin. */ |

| #define | DIFF_P_INT_ROUTE1_P_WCHG_INT1 ((uint8_t) 0x00) /* Interrupt routed to INT1 pin. */ |

| #define | DIFF_P_INT_ROUTE1_P_TGT2_INT2 ((uint8_t) 0x04) /* Interrupt routed to INT2 pin. */ |

| #define | DIFF_P_INT_ROUTE1_P_TGT2_INT1 ((uint8_t) 0x00) /* Interrupt routed to INT1 pin. */ |

| #define | DIFF_P_INT_ROUTE1_P_TGT1_INT2 ((uint8_t) 0x08) /* Interrupt routed to INT2 pin. */ |

| #define | DIFF_P_INT_ROUTE1_P_TGT1_INT1 ((uint8_t) 0x00) /* Interrupt routed to INT1 pin. */ |

| #define | DIFF_P_INT_ROUTE1_P_TGT0_INT2 ((uint8_t) 0x10) /* Interrupt routed to INT2 pin. */ |

| #define | DIFF_P_INT_ROUTE1_P_TGT0_INT1 ((uint8_t) 0x00) /* Interrupt routed to INT1 pin. */ |

| #define | DIFF_P_INT_ROUTE1_T_TGT_INT2 ((uint8_t) 0x20) /* Interrupt routed to INT2 pin. */ |

| #define | DIFF_P_INT_ROUTE1_T_TGT_INT1 ((uint8_t) 0x00) /* Interrupt routed to INT1 pin. */ |

| #define | DIFF_P_INT_ROUTE1_TDU_INT2 ((uint8_t) 0x40) /* Interrupt routed to INT2 pin. */ |

| #define | DIFF_P_INT_ROUTE1_TDU_INT1 ((uint8_t) 0x00) /* Interrupt routed to INT1 pin. */ |

| #define | DIFF_P_INT_ROUTE1_TDO_INT2 ((uint8_t) 0x80) /* Interrupt routed to INT2 pin. */ |

| #define | DIFF_P_INT_ROUTE1_TDO_INT1 ((uint8_t) 0x00) /* Interrupt routed to INT1 pin. */ |

The diff_p.h contains the DIFF_P Pressure sensor register definitions, access macros, and its bit mask.

Definition in file diff_p.h.

| #define DIFF_P_CTRL_REG1_OSR_OSR1 ((uint8_t) 0x00) /* Oversampling Rate#1. */ |

| #define DIFF_P_CTRL_REG1_OSR_OSR1024 ((uint8_t) 0x58) /* Oversampling Rate#1024. */ |

| #define DIFF_P_CTRL_REG1_OSR_OSR128 ((uint8_t) 0x38) /* Oversampling Rate#128. */ |

| #define DIFF_P_CTRL_REG1_OSR_OSR1280 ((uint8_t) 0x60) /* Oversampling Rate#1280. */ |

| #define DIFF_P_CTRL_REG1_OSR_OSR1536 ((uint8_t) 0x68) /* Oversampling Rate#1536. */ |

| #define DIFF_P_CTRL_REG1_OSR_OSR16 ((uint8_t) 0x20) /* Oversampling Rate#16. */ |

| #define DIFF_P_CTRL_REG1_OSR_OSR2 ((uint8_t) 0x08) /* Oversampling Rate#2. */ |

| #define DIFF_P_CTRL_REG1_OSR_OSR2048 ((uint8_t) 0x70) /* Oversampling Rate#2048. */ |

| #define DIFF_P_CTRL_REG1_OSR_OSR256 ((uint8_t) 0x40) /* Oversampling Rate#256. */ |

| #define DIFF_P_CTRL_REG1_OSR_OSR2560 ((uint8_t) 0x78) /* Oversampling Rate#2560. */ |

| #define DIFF_P_CTRL_REG1_OSR_OSR3072 ((uint8_t) 0x80) /* Oversampling Rate#3072. */ |

| #define DIFF_P_CTRL_REG1_OSR_OSR32 ((uint8_t) 0x28) /* Oversampling Rate#32. */ |

| #define DIFF_P_CTRL_REG1_OSR_OSR4 ((uint8_t) 0x10) /* Oversampling Rate#4. */ |

| #define DIFF_P_CTRL_REG1_OSR_OSR4096 ((uint8_t) 0x88) /* Oversampling Rate#4096. */ |

| #define DIFF_P_CTRL_REG1_OSR_OSR512 ((uint8_t) 0x48) /* Oversampling Rate#512. */ |

| #define DIFF_P_CTRL_REG1_OSR_OSR5120 ((uint8_t) 0x90) /* Oversampling Rate#5120. */ |

| #define DIFF_P_CTRL_REG1_OSR_OSR6144 ((uint8_t) 0x98) /* Oversampling Rate#6144. */ |

| #define DIFF_P_CTRL_REG1_OSR_OSR64 ((uint8_t) 0x30) /* Oversampling Rate#64. */ |

| #define DIFF_P_CTRL_REG1_OSR_OSR7168 ((uint8_t) 0xa0) /* Oversampling Rate#7168. */ |

| #define DIFF_P_CTRL_REG1_OSR_OSR768 ((uint8_t) 0x50) /* Oversampling Rate#768. */ |

| #define DIFF_P_CTRL_REG1_OSR_OSR8 ((uint8_t) 0x18) /* Oversampling Rate#8. */ |

| #define DIFF_P_CTRL_REG1_OSR_OSR8192 ((uint8_t) 0xa8) /* Oversampling Rate#8192. */ |

| #define DIFF_P_CTRL_REG1_OST_NORMAL ((uint8_t) 0x00) /* Normal operating mode. */ |

| #define DIFF_P_CTRL_REG1_OST_ONESHOT ((uint8_t) 0x02) /* One Shot Mode. */ |

| #define DIFF_P_CTRL_REG1_RST_MASK ((uint8_t) 0x04) |

Definition at line 706 of file diff_p.h.

Referenced by DIFF_P_I2C_DeInit(), and DIFF_P_SPI_DeInit().

| #define DIFF_P_CTRL_REG1_RST_NORMAL ((uint8_t) 0x00) /* Normal operating mode. */ |

| #define DIFF_P_CTRL_REG1_RST_RESET ((uint8_t) 0x04) /* Device will be reset. */ |

Definition at line 720 of file diff_p.h.

Referenced by DIFF_P_I2C_DeInit(), and DIFF_P_SPI_DeInit().

| #define DIFF_P_CTRL_REG1_SBYB_ACTIVE ((uint8_t) 0x01) /* Part is ACTIVE. */ |

Definition at line 716 of file diff_p.h.

Referenced by DIFF_P_I2C_Configure(), and DIFF_P_SPI_Configure().

| #define DIFF_P_CTRL_REG1_SBYB_MASK ((uint8_t) 0x01) |

Definition at line 700 of file diff_p.h.

Referenced by DIFF_P_I2C_Configure(), DIFF_P_I2C_Initialize(), DIFF_P_SPI_Configure(), and DIFF_P_SPI_Initialize().

| #define DIFF_P_CTRL_REG1_SBYB_STANDBY ((uint8_t) 0x00) /* Part is in STANDBY mode. */ |

Definition at line 717 of file diff_p.h.

Referenced by DIFF_P_I2C_Configure(), DIFF_P_I2C_Initialize(), DIFF_P_SPI_Configure(), and DIFF_P_SPI_Initialize().

| #define DIFF_P_CTRL_REG2_BRWNOUT_EN_DISABLED ((uint8_t) 0x00) /* Internal brown out circuit is disabled. */ |

| #define DIFF_P_CTRL_REG2_BRWNOUT_EN_ENABLED ((uint8_t) 0x40) /* Internal brown out circuit is enabled. */ |

| #define DIFF_P_CTRL_REG2_CTRL_AC_CALRUN ((uint8_t) 0x80) /* Run Calibration Algorithm. */ |

Definition at line 807 of file diff_p.h.

Referenced by DIFF_P_I2C_Initialize(), and DIFF_P_SPI_Initialize().

| #define DIFF_P_CTRL_REG2_CTRL_AC_MASK ((uint8_t) 0x80) |

Definition at line 783 of file diff_p.h.

Referenced by DIFF_P_I2C_Initialize(), and DIFF_P_SPI_Initialize().

| #define DIFF_P_CTRL_REG2_CTRL_AC_NOCALRUN ((uint8_t) 0x00) /* Calibration Algorithm not run. */ |

| #define DIFF_P_CTRL_REG2_F_READ_FASTREAD ((uint8_t) 0x00) /* Loops between register address 0x00 and 0x04. */ |

| #define DIFF_P_CTRL_REG2_F_READ_NORMAL ((uint8_t) 0x20) /* Loops between all register addresses. */ |

| #define DIFF_P_CTRL_REG2_ODR_ODR0P781 ((uint8_t) 0x0c) /* Output Data Rate#0.781. */ |

| #define DIFF_P_CTRL_REG2_ODR_ODR100 ((uint8_t) 0x05) /* Output Data Rate#100. */ |

| #define DIFF_P_CTRL_REG2_ODR_ODR12P5 ((uint8_t) 0x08) /* Output Data Rate#12.5. */ |

| #define DIFF_P_CTRL_REG2_ODR_ODR1600 ((uint8_t) 0x01) /* Output Data Rate#1600. */ |

| #define DIFF_P_CTRL_REG2_ODR_ODR1P563 ((uint8_t) 0x0b) /* Output Data Rate#1.563. */ |

| #define DIFF_P_CTRL_REG2_ODR_ODR200 ((uint8_t) 0x04) /* Output Data Rate#200. */ |

| #define DIFF_P_CTRL_REG2_ODR_ODR25 ((uint8_t) 0x07) /* Output Data Rate#25. */ |

| #define DIFF_P_CTRL_REG2_ODR_ODR3200 ((uint8_t) 0x00) /* Output Data Rate#3200. */ |

| #define DIFF_P_CTRL_REG2_ODR_ODR3P125 ((uint8_t) 0x0a) /* Output Data Rate#3.125. */ |

| #define DIFF_P_CTRL_REG2_ODR_ODR400 ((uint8_t) 0x03) /* Output Data Rate#400. */ |

| #define DIFF_P_CTRL_REG2_ODR_ODR50 ((uint8_t) 0x06) /* Output Data Rate#50. */ |

| #define DIFF_P_CTRL_REG2_ODR_ODR6P25 ((uint8_t) 0x09) /* Output Data Rate#6.25. */ |

| #define DIFF_P_CTRL_REG2_ODR_ODR800 ((uint8_t) 0x02) /* Output Data Rate#800. */ |

| #define DIFF_P_CTRL_REG3_IPOL1_ACTIVE_HIGH ((uint8_t) 0x20) /* Active High. */ |

| #define DIFF_P_CTRL_REG3_IPOL1_ACTIVE_LOW ((uint8_t) 0x00) /* Active Low. */ |

| #define DIFF_P_CTRL_REG3_IPOL2_ACTIVE_HIGH ((uint8_t) 0x02) /* Active High. */ |

| #define DIFF_P_CTRL_REG3_IPOL2_ACTIVE_LOW ((uint8_t) 0x00) /* Active Low. */ |

| #define DIFF_P_CTRL_REG3_PP_OD1_OPENDRAIN ((uint8_t) 0x10) /* Open drain. */ |

| #define DIFF_P_CTRL_REG3_PP_OD1_PUSHPULL ((uint8_t) 0x00) /* Push-pull. */ |

| #define DIFF_P_CTRL_REG3_PP_OD2_OPENDRAIN ((uint8_t) 0x01) /* Open drain. */ |

| #define DIFF_P_CTRL_REG3_PP_OD2_PUSHPULL ((uint8_t) 0x00) /* Push-pull. */ |

| #define DIFF_P_INT_MASK0_PDO_INT_EN ((uint8_t) 0x02) /* Interrupt Enabled. */ |

| #define DIFF_P_INT_MASK0_PDR_INT_EN ((uint8_t) 0x20) /* Interrupt Enabled. */ |

| #define DIFF_P_INT_MASK0_PDU_INT_EN ((uint8_t) 0x01) /* Interrupt Enabled. */ |

| #define DIFF_P_INT_MASK0_POW_INT_EN ((uint8_t) 0x80) /* Interrupt Enabled. */ |

| #define DIFF_P_INT_MASK0_TDR_INT_EN ((uint8_t) 0x10) /* Interrupt Enabled. */ |

| #define DIFF_P_INT_MASK0_TOW_INT_EN ((uint8_t) 0x40) /* Interrupt Enabled. */ |

| #define DIFF_P_INT_MASK0_VERRA_INT_EN ((uint8_t) 0x08) /* Interrupt Enabled. */ |

| #define DIFF_P_INT_MASK1_P_TGT0_INT_EN ((uint8_t) 0x10) /* Interrupt Enabled. */ |

| #define DIFF_P_INT_MASK1_P_TGT1_INT_EN ((uint8_t) 0x08) /* Interrupt Enabled. */ |

| #define DIFF_P_INT_MASK1_P_TGT2_INT_EN ((uint8_t) 0x04) /* Interrupt Enabled. */ |

| #define DIFF_P_INT_MASK1_P_WCHG_INT_EN ((uint8_t) 0x02) /* Interrupt Enabled. */ |

| #define DIFF_P_INT_MASK1_T_TGT_INT_EN ((uint8_t) 0x20) /* Interrupt Enabled. */ |

| #define DIFF_P_INT_MASK1_TDO_INT_EN ((uint8_t) 0x80) /* Interrupt Enabled. */ |

| #define DIFF_P_INT_MASK1_TDU_INT_EN ((uint8_t) 0x40) /* Interrupt Enabled. */ |

| #define DIFF_P_INT_ROUTE0_PDO_INT1 ((uint8_t) 0x00) /* Interrupt routed to INT1 pin. */ |

| #define DIFF_P_INT_ROUTE0_PDO_INT2 ((uint8_t) 0x02) /* Interrupt routed to INT2 pin. */ |

| #define DIFF_P_INT_ROUTE0_PDR_INT1 ((uint8_t) 0x00) /* Interrupt routed to INT1 pin. */ |

| #define DIFF_P_INT_ROUTE0_PDR_INT2 ((uint8_t) 0x20) /* Interrupt routed to INT2 pin. */ |

| #define DIFF_P_INT_ROUTE0_PDU_INT1 ((uint8_t) 0x00) /* Interrupt routed to INT1 pin. */ |

| #define DIFF_P_INT_ROUTE0_PDU_INT2 ((uint8_t) 0x01) /* Interrupt routed to INT2 pin. */ |

| #define DIFF_P_INT_ROUTE0_POW_INT1 ((uint8_t) 0x00) /* Interrupt routed to INT1 pin. */ |

| #define DIFF_P_INT_ROUTE0_POW_INT2 ((uint8_t) 0x80) /* Interrupt routed to INT2 pin. */ |

| #define DIFF_P_INT_ROUTE0_TDR_INT1 ((uint8_t) 0x00) /* Interrupt routed to INT1 pin. */ |

| #define DIFF_P_INT_ROUTE0_TDR_INT2 ((uint8_t) 0x10) /* Interrupt routed to INT2 pin. */ |

| #define DIFF_P_INT_ROUTE0_TOW_INT1 ((uint8_t) 0x00) /* Interrupt routed to INT1 pin. */ |

| #define DIFF_P_INT_ROUTE0_TOW_INT2 ((uint8_t) 0x40) /* Interrupt routed to INT2 pin. */ |

| #define DIFF_P_INT_ROUTE0_VERRA_INT1 ((uint8_t) 0x00) /* Interrupt routed to INT1 pin. */ |

| #define DIFF_P_INT_ROUTE0_VERRA_INT2 ((uint8_t) 0x08) /* Interrupt routed to INT2 pin. */ |

| #define DIFF_P_INT_ROUTE1_P_TGT0_INT1 ((uint8_t) 0x00) /* Interrupt routed to INT1 pin. */ |

| #define DIFF_P_INT_ROUTE1_P_TGT0_INT2 ((uint8_t) 0x10) /* Interrupt routed to INT2 pin. */ |

| #define DIFF_P_INT_ROUTE1_P_TGT1_INT1 ((uint8_t) 0x00) /* Interrupt routed to INT1 pin. */ |

| #define DIFF_P_INT_ROUTE1_P_TGT1_INT2 ((uint8_t) 0x08) /* Interrupt routed to INT2 pin. */ |

| #define DIFF_P_INT_ROUTE1_P_TGT2_INT1 ((uint8_t) 0x00) /* Interrupt routed to INT1 pin. */ |

| #define DIFF_P_INT_ROUTE1_P_TGT2_INT2 ((uint8_t) 0x04) /* Interrupt routed to INT2 pin. */ |

| #define DIFF_P_INT_ROUTE1_P_WCHG_INT1 ((uint8_t) 0x00) /* Interrupt routed to INT1 pin. */ |

| #define DIFF_P_INT_ROUTE1_P_WCHG_INT2 ((uint8_t) 0x02) /* Interrupt routed to INT2 pin. */ |

| #define DIFF_P_INT_ROUTE1_T_TGT_INT1 ((uint8_t) 0x00) /* Interrupt routed to INT1 pin. */ |

| #define DIFF_P_INT_ROUTE1_T_TGT_INT2 ((uint8_t) 0x20) /* Interrupt routed to INT2 pin. */ |

| #define DIFF_P_INT_ROUTE1_TDO_INT1 ((uint8_t) 0x00) /* Interrupt routed to INT1 pin. */ |

| #define DIFF_P_INT_ROUTE1_TDO_INT2 ((uint8_t) 0x80) /* Interrupt routed to INT2 pin. */ |

| #define DIFF_P_INT_ROUTE1_TDU_INT1 ((uint8_t) 0x00) /* Interrupt routed to INT1 pin. */ |

| #define DIFF_P_INT_ROUTE1_TDU_INT2 ((uint8_t) 0x40) /* Interrupt routed to INT2 pin. */ |

| #define DIFF_P_INT_STATUS_0_PDO_NO_OVERFLOW ((uint8_t) 0x00) /* No overflow occurred. */ |

| #define DIFF_P_INT_STATUS_0_PDO_OVERFLOW ((uint8_t) 0x02) /* Overflow occurred. */ |

| #define DIFF_P_INT_STATUS_0_PDR_DRDY ((uint8_t) 0x20) /* A new set of Pressure data is ready. */ |

| #define DIFF_P_INT_STATUS_0_PDR_MASK ((uint8_t) 0x20) |

| #define DIFF_P_INT_STATUS_0_PDU_NO_UNDERFLOW ((uint8_t) 0x00) /* No Underflow occurred. */ |

| #define DIFF_P_INT_STATUS_0_PDU_UNDERFLOW ((uint8_t) 0x01) /* Underflow occurred. */ |

| #define DIFF_P_INT_STATUS_0_POW_OWR ((uint8_t) 0x80) /* Previous Pressure data was overwritten by new */ |

| #define DIFF_P_INT_STATUS_0_TDR_DRDY ((uint8_t) 0x10) /* A new Temperature data is ready. */ |

| #define DIFF_P_INT_STATUS_0_TDR_MASK ((uint8_t) 0x10) |

| #define DIFF_P_INT_STATUS_0_TOW_OWR ((uint8_t) 0x40) /* Previous Temperature data was overwritten by new */ |

| #define DIFF_P_INT_STATUS_0_VERRA_BRWNOUT ((uint8_t) 0x08) /* Analog voltage brownout occurred. */ |

| #define DIFF_P_INT_STATUS_0_VERRA_NO_BRWNOUT ((uint8_t) 0x00) /* No brownout occurred. */ |

| #define DIFF_P_INT_STATUS_1_P_TGT0_MASK ((uint8_t) 0x10) |

| #define DIFF_P_INT_STATUS_1_P_TGT0_REACHED ((uint8_t) 0x10) /* Temperature target reached. */ |

| #define DIFF_P_INT_STATUS_1_P_TGT1_REACHED ((uint8_t) 0x08) /* Temperature target reached. */ |

| #define DIFF_P_INT_STATUS_1_P_TGT2_REACHED ((uint8_t) 0x04) /* Temperature target reached. */ |

| #define DIFF_P_INT_STATUS_1_P_WCHG_TH_CROSSED ((uint8_t) 0x02) /* pressure has crossed the window threshold defined */ |

| #define DIFF_P_INT_STATUS_1_T_TGT_REACHED ((uint8_t) 0x20) /* Temperature target reached. */ |

| #define DIFF_P_INT_STATUS_1_TDO_NO_OVERFLOW ((uint8_t) 0x00) /* No overflow occurred. */ |

| #define DIFF_P_INT_STATUS_1_TDO_OVERFLOW ((uint8_t) 0x80) /* Overflow occurred. */ |

| #define DIFF_P_INT_STATUS_1_TDU_NO_UNDERFLOW ((uint8_t) 0x00) /* No Underflow occurred. */ |

| #define DIFF_P_INT_STATUS_1_TDU_UNDERFLOW ((uint8_t) 0x40) /* Underflow occurred. */ |

| #define DIFF_P_NPS3000VV_WHOAMI_VALUE (0xD0) /* DIFF_P Who_Am_I Value of Part Number NPS3000VV. */ |

| #define DIFF_P_NPS3001DV_WHOAMI_VALUE (0xD1) /* DIFF_P Who_Am_I Value of Part Number NPS3001DV. */ |

| #define DIFF_P_NPS3002VV_WHOAMI_VALUE (0xD2) /* DIFF_P Who_Am_I Value of Part Number NPS3000VV. */ |

| #define DIFF_P_NPS3005DV_WHOAMI_VALUE (0xD3) /* DIFF_P Who_Am_I Value of Part Number NPS3000VV. */ |

| #define DIFF_P_STATUS_ACTIVE_MODE_ACTIVE ((uint8_t) 0x80) /* Sensor is in active mode. */ |

| #define DIFF_P_STATUS_ACTIVE_MODE_STANDBY ((uint8_t) 0x00) /* Sensor is in standby mode. */ |

| #define DIFF_P_STATUS_I2C_RPG_CNT_CAN_RPG ((uint8_t) 0x00) /* I2C address can be reprogrammed. */ |

| #define DIFF_P_STATUS_I2C_RPG_CNT_CANT_RPG ((uint8_t) 0x40) /* I2C address cannot be reprogrammed. */ |

| #define DIFF_P_STATUS_I2C_RPG_NO_RPG ((uint8_t) 0x00) /* No Reprograming has taken place. */ |

| #define DIFF_P_STATUS_I2C_RPG_RPG_SUCCESS ((uint8_t) 0x20) /* I2C Reprograming successful. */ |

| #define DIFF_P_STATUS_I2C_RPG_STATUS_RPG_CPLT ((uint8_t) 0x00) /* Reprograming cycle completed. */ |

| #define DIFF_P_STATUS_I2C_RPG_STATUS_RPG_INIT ((uint8_t) 0x10) /* Reprograming cycle initiated. */ |

| #define DIFF_P_STATUS_OSR_ERR_ERR ((uint8_t) 0x02) /* Illegal ODR/OSR combination. */ |

| #define DIFF_P_STATUS_OSR_ERR_NO_ERR ((uint8_t) 0x00) /* No Error. */ |

| #define DIFF_P_STATUS_RST_STATUS_NO_RST ((uint8_t) 0x00) /* No POR, brownout or soft reset has occurred. */ |

| #define DIFF_P_STATUS_RST_STATUS_RST ((uint8_t) 0x01) /* Part has come out of POR, brownout or soft reset. */ |

| #define DIFF_P_STATUS_STAT_CPLT_NO_SUCCESS ((uint8_t) 0x00) /* Calibration routine was not successful. */ |

| #define DIFF_P_STATUS_STAT_CPLT_SUCCESS ((uint8_t) 0x04) /* Calibration routine was successful. */ |

| #define DIFF_P_STATUS_STAT_EP_DETECTED ((uint8_t) 0x08) /* Existing pressure has been detected. */ |

| #define DIFF_P_STATUS_STAT_EP_MASK ((uint8_t) 0x08) |

Definition at line 515 of file diff_p.h.

Referenced by DIFF_P_I2C_Initialize(), and DIFF_P_SPI_Initialize().

| #define DIFF_P_STATUS_STAT_EP_NOTDETECTED ((uint8_t) 0x00) /* No existing pressure detected. */ |

| typedef uint8_t DIFF_P_I2C_ADDRESS_t |

| typedef uint8_t DIFF_P_OFF_CAL_P_LSB_t |

| typedef uint8_t DIFF_P_OFF_CAL_P_MSB_t |

| typedef uint8_t DIFF_P_OFF_MOP_LSB_t |

| typedef uint8_t DIFF_P_OFF_MOP_MSB_t |

| typedef uint8_t DIFF_P_OFF_P_LSB_t |

| typedef uint8_t DIFF_P_OFF_P_MSB_t |

| typedef uint8_t DIFF_P_OFF_T_t |

| typedef uint8_t DIFF_P_OUT_P_LSB_t |

| typedef uint8_t DIFF_P_OUT_P_MSB_t |

| typedef uint8_t DIFF_P_OUT_T_t |

| typedef uint8_t DIFF_P_P_MAX_LSB_t |

| typedef uint8_t DIFF_P_P_MAX_MSB_t |

| typedef uint8_t DIFF_P_P_MIN_LSB_t |

| typedef uint8_t DIFF_P_P_MIN_MSB_t |

| typedef uint8_t DIFF_P_P_TGT0_LSB_t |

| typedef uint8_t DIFF_P_P_TGT0_MSB_t |

| typedef uint8_t DIFF_P_P_TGT1_LSB_t |

| typedef uint8_t DIFF_P_P_TGT1_MSB_t |

| typedef uint8_t DIFF_P_P_TGT2_LSB_t |

| typedef uint8_t DIFF_P_P_TGT2_MSB_t |

| typedef uint8_t DIFF_P_PROD_REV_t |

| typedef uint8_t DIFF_P_SERIALNUMBER_BYTE0_t |

| typedef uint8_t DIFF_P_SERIALNUMBER_BYTE1_t |

| typedef uint8_t DIFF_P_SERIALNUMBER_BYTE2_t |

| typedef uint8_t DIFF_P_SERIALNUMBER_BYTE3_t |

| typedef uint8_t DIFF_P_SERIALNUMBER_BYTE4_t |

| typedef uint8_t DIFF_P_SERIALNUMBER_BYTE5_t |

| typedef uint8_t DIFF_P_SERIALNUMBER_BYTE6_t |

| typedef uint8_t DIFF_P_SERIALNUMBER_BYTE7_t |

| typedef uint8_t DIFF_P_T_MAX_t |

| typedef uint8_t DIFF_P_T_MIN_t |

| typedef uint8_t DIFF_P_T_TGT_t |

| typedef uint8_t DIFF_P_WHO_AM_I_t |

| anonymous enum |

DIFF_P Sensor Internal Registers