|

ISSDK

1.7

IoT Sensing Software Development Kit

|

|

ISSDK

1.7

IoT Sensing Software Development Kit

|

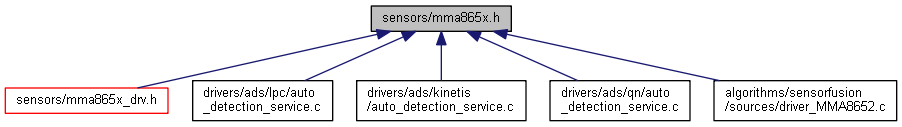

The mma865x.h contains the MMA865xFC Digital Accelerometer Sensor register definitions, access macros, and device access functions. More...

Go to the source code of this file.

Data Structures | |

| union | MMA865x_STATUS_t |

| union | MMA865x_F_STATUS_t |

| union | MMA865x_F_SETUP_t |

| union | MMA865x_TRIG_CFG_t |

| union | MMA865x_SYSMOD_t |

| union | MMA865x_INT_SOURCE_t |

| union | MMA865x_XYZ_DATA_CFG_t |

| union | MMA865x_HP_FILTER_CUTOFF_t |

| union | MMA865x_PL_STATUS_t |

| union | MMA865x_PL_CFG_t |

| union | MMA865x_PL_BF_ZCOMP_t |

| union | MMA865x_P_L_THS_REG_t |

| union | MMA865x_FF_MT_CFG_t |

| union | MMA865x_FF_MT_SRC_t |

| union | MMA865x_FF_MT_THS_t |

| union | MMA865x_TRANSIENT_CFG_t |

| union | MMA865x_TRANSIENT_SRC_t |

| union | MMA865x_TRANSIENT_THS_t |

| union | MMA865x_PULSE_CFG_t |

| union | MMA865x_PULSE_SRC_t |

| union | MMA865x_PULSE_THSX_t |

| union | MMA865x_PULSE_THSY_t |

| union | MMA865x_PULSE_THSZ_t |

| union | MMA865x_CTRL_REG1_t |

| union | MMA865x_CTRL_REG2_t |

| union | MMA865x_CTRL_REG3_t |

| union | MMA865x_CTRL_REG4_t |

| union | MMA865x_CTRL_REG5_t |

Macros | |

| #define | MMA865x_I2C_ADDRESS (0x1D) /* MMA865x I2C Slave Address. */ |

| #define | MMA8652_WHOAMI_VALUE (0x4A) /* MMA8652 Who_Am_I Value. */ |

| #define | MMA8653_WHOAMI_VALUE (0x5A) /* MMA8653 Who_Am_I Value. */ |

| #define | MMA865x_STATUS_XDR_MASK ((uint8_t) 0x01) |

| #define | MMA865x_STATUS_XDR_SHIFT ((uint8_t) 0) |

| #define | MMA865x_STATUS_YDR_MASK ((uint8_t) 0x02) |

| #define | MMA865x_STATUS_YDR_SHIFT ((uint8_t) 1) |

| #define | MMA865x_STATUS_ZDR_MASK ((uint8_t) 0x04) |

| #define | MMA865x_STATUS_ZDR_SHIFT ((uint8_t) 2) |

| #define | MMA865x_STATUS_ZYXDR_MASK ((uint8_t) 0x08) |

| #define | MMA865x_STATUS_ZYXDR_SHIFT ((uint8_t) 3) |

| #define | MMA865x_STATUS_XOW_MASK ((uint8_t) 0x10) |

| #define | MMA865x_STATUS_XOW_SHIFT ((uint8_t) 4) |

| #define | MMA865x_STATUS_YOW_MASK ((uint8_t) 0x20) |

| #define | MMA865x_STATUS_YOW_SHIFT ((uint8_t) 5) |

| #define | MMA865x_STATUS_ZOW_MASK ((uint8_t) 0x40) |

| #define | MMA865x_STATUS_ZOW_SHIFT ((uint8_t) 6) |

| #define | MMA865x_STATUS_ZYXOW_MASK ((uint8_t) 0x80) |

| #define | MMA865x_STATUS_ZYXOW_SHIFT ((uint8_t) 7) |

| #define | MMA865x_STATUS_XDR_DRDY ((uint8_t) 0x01) /* - Set to 1 whenever new X-axis data acquisition is */ |

| #define | MMA865x_STATUS_YDR_DRDY ((uint8_t) 0x02) /* - Set to 1 whenever new Y-axis data acquisition is */ |

| #define | MMA865x_STATUS_ZDR_DRDY ((uint8_t) 0x04) /* - Set to 1 whenever new Z-axis data acquisition is */ |

| #define | MMA865x_STATUS_ZYXDR_DRDY ((uint8_t) 0x08) /* - Signals that new acquisition for any of the enabled */ |

| #define | MMA865x_STATUS_XOW_OWR ((uint8_t) 0x10) /* - Set to 1 whenever new X-axis acquisition is */ |

| #define | MMA865x_STATUS_YOW_OWR ((uint8_t) 0x20) /* - Set to 1 whenever new Y-axis acquisition is */ |

| #define | MMA865x_STATUS_ZOW_OWR ((uint8_t) 0x40) /* - Set to 1 whenever new Z-axis acquisition is */ |

| #define | MMA865x_STATUS_ZYXOW_OWR ((uint8_t) 0x80) /* - Set to 1 whenever new data is acquired before */ |

| #define | MMA865x_F_STATUS_F_CNT_MASK ((uint8_t) 0x3F) |

| #define | MMA865x_F_STATUS_F_CNT_SHIFT ((uint8_t) 0) |

| #define | MMA865x_F_STATUS_F_WMKF_MASK ((uint8_t) 0x40) |

| #define | MMA865x_F_STATUS_F_WMKF_SHIFT ((uint8_t) 6) |

| #define | MMA865x_F_STATUS_F_OVF_MASK ((uint8_t) 0x80) |

| #define | MMA865x_F_STATUS_F_OVF_SHIFT ((uint8_t) 7) |

| #define | MMA865x_F_STATUS_F_WMKF_NONE ((uint8_t) 0x00) /* - FIFO Watermark event has NOT been detected. */ |

| #define | MMA865x_F_STATUS_F_WMKF_DETECTED ((uint8_t) 0x40) /* - FIFO Watermark event has been detected. */ |

| #define | MMA865x_F_STATUS_F_OVF_NONE ((uint8_t) 0x00) /* - FIFO Overflow event has NOT been detected. */ |

| #define | MMA865x_F_STATUS_F_OVF_DETECTED ((uint8_t) 0x80) /* - FIFO Overflow event has been detected. */ |

| #define | MMA865x_F_SETUP_F_WMRK_MASK ((uint8_t) 0x3F) |

| #define | MMA865x_F_SETUP_F_WMRK_SHIFT ((uint8_t) 0) |

| #define | MMA865x_F_SETUP_F_MODE_MASK ((uint8_t) 0xC0) |

| #define | MMA865x_F_SETUP_F_MODE_SHIFT ((uint8_t) 6) |

| #define | MMA865x_F_SETUP_F_MODE_FIFO_OFF ((uint8_t) 0x00) /* - FIFO is disabled. */ |

| #define | MMA865x_F_SETUP_F_MODE_CIR_MODE ((uint8_t) 0x40) /* - FIFO is in Circular Buffer mode. */ |

| #define | MMA865x_F_SETUP_F_MODE_STOP_MODE ((uint8_t) 0x80) /* - FIFO is in Stop mode. */ |

| #define | MMA865x_F_SETUP_F_MODE_TRIG_MODE ((uint8_t) 0xc0) /* - FIFO is in Trigger mode. The FIFO will be in a */ |

| #define | MMA865x_TRIG_CFG_TRIG_FF_MT_MASK ((uint8_t) 0x04) |

| #define | MMA865x_TRIG_CFG_TRIG_FF_MT_SHIFT ((uint8_t) 2) |

| #define | MMA865x_TRIG_CFG_TRIG_PULSE_MASK ((uint8_t) 0x08) |

| #define | MMA865x_TRIG_CFG_TRIG_PULSE_SHIFT ((uint8_t) 3) |

| #define | MMA865x_TRIG_CFG_TRIG_LNDPRT_MASK ((uint8_t) 0x10) |

| #define | MMA865x_TRIG_CFG_TRIG_LNDPRT_SHIFT ((uint8_t) 4) |

| #define | MMA865x_TRIG_CFG_TRIG_TRANS_MASK ((uint8_t) 0x20) |

| #define | MMA865x_TRIG_CFG_TRIG_TRANS_SHIFT ((uint8_t) 5) |

| #define | MMA865x_TRIG_CFG_TRIG_TRANS_EN ((uint8_t) 0x20) /* - This function can trigger the FIFO at its (the */ |

| #define | MMA865x_TRIG_CFG_TRIG_TRANS_DISABLED ((uint8_t) 0x00) /* - This function has not asserted its interrupt. */ |

| #define | MMA865x_TRIG_CFG_TRIG_LNDPRT_EN ((uint8_t) 0x10) /* - This function can trigger the FIFO at its (the */ |

| #define | MMA865x_TRIG_CFG_TRIG_LNDPRT_DISABLED ((uint8_t) 0x00) /* - This function has not asserted its interrupt. */ |

| #define | MMA865x_TRIG_CFG_TRIG_PULSE_EN ((uint8_t) 0x08) /* - This function can trigger the FIFO at its (the */ |

| #define | MMA865x_TRIG_CFG_TRIG_PULSE_DISABLED ((uint8_t) 0x00) /* - This function has not asserted its interrupt. */ |

| #define | MMA865x_TRIG_CFG_TRIG_FF_MT_EN ((uint8_t) 0x04) /* - This function can trigger the FIFO at its (the */ |

| #define | MMA865x_TRIG_CFG_TRIG_FF_MT_DISABLED ((uint8_t) 0x00) /* - This function has not asserted its interrupt. */ |

| #define | MMA865x_SYSMOD_SYSMOD_MASK ((uint8_t) 0x03) |

| #define | MMA865x_SYSMOD_SYSMOD_SHIFT ((uint8_t) 0) |

| #define | MMA865x_SYSMOD_FGT_MASK ((uint8_t) 0x7C) |

| #define | MMA865x_SYSMOD_FGT_SHIFT ((uint8_t) 2) |

| #define | MMA865x_SYSMOD_FGERR_MASK ((uint8_t) 0x80) |

| #define | MMA865x_SYSMOD_FGERR_SHIFT ((uint8_t) 7) |

| #define | MMA865x_SYSMOD_FGERR_NONE ((uint8_t) 0x00) /* - No FIFO Gate Error detected. */ |

| #define | MMA865x_SYSMOD_FGERR_DETECTED ((uint8_t) 0x80) /* - FIFO Gate Error was detected. */ |

| #define | MMA865x_SYSMOD_SYSMOD_STANDBY ((uint8_t) 0x00) /* - STANDBY Mode. */ |

| #define | MMA865x_SYSMOD_SYSMOD_WAKE ((uint8_t) 0x01) /* - WAKE Mode. */ |

| #define | MMA865x_SYSMOD_SYSMOD_SLEEP ((uint8_t) 0x02) /* - SLEEP Mode. */ |

| #define | MMA865x_INT_SOURCE_SRC_DRDY_MASK ((uint8_t) 0x01) |

| #define | MMA865x_INT_SOURCE_SRC_DRDY_SHIFT ((uint8_t) 0) |

| #define | MMA865x_INT_SOURCE_SRC_FF_MT_MASK ((uint8_t) 0x04) |

| #define | MMA865x_INT_SOURCE_SRC_FF_MT_SHIFT ((uint8_t) 2) |

| #define | MMA865x_INT_SOURCE_SRC_PULSE_MASK ((uint8_t) 0x08) |

| #define | MMA865x_INT_SOURCE_SRC_PULSE_SHIFT ((uint8_t) 3) |

| #define | MMA865x_INT_SOURCE_SRC_LNDPRT_MASK ((uint8_t) 0x10) |

| #define | MMA865x_INT_SOURCE_SRC_LNDPRT_SHIFT ((uint8_t) 4) |

| #define | MMA865x_INT_SOURCE_SRC_TRANS_MASK ((uint8_t) 0x20) |

| #define | MMA865x_INT_SOURCE_SRC_TRANS_SHIFT ((uint8_t) 5) |

| #define | MMA865x_INT_SOURCE_SRC_FIFO_MASK ((uint8_t) 0x40) |

| #define | MMA865x_INT_SOURCE_SRC_FIFO_SHIFT ((uint8_t) 6) |

| #define | MMA865x_INT_SOURCE_SRC_ASLP_MASK ((uint8_t) 0x80) |

| #define | MMA865x_INT_SOURCE_SRC_ASLP_SHIFT ((uint8_t) 7) |

| #define | MMA865x_INT_SOURCE_SRC_ASLP_READY ((uint8_t) 0x80) /* - An interrupt event that can cause a */ |

| #define | MMA865x_INT_SOURCE_SRC_ASLP_INACTIVE ((uint8_t) 0x00) /* - No WAKE-to-SLEEP or SLEEP-to-WAKE system mode */ |

| #define | MMA865x_INT_SOURCE_SRC_FIFO_READY ((uint8_t) 0x40) /* - A FIFO interrupt event (such as an overflow */ |

| #define | MMA865x_INT_SOURCE_SRC_FIFO_INACTIVE ((uint8_t) 0x00) /* - No FIFO interrupt event has occurred. */ |

| #define | MMA865x_INT_SOURCE_SRC_TRANS_READY ((uint8_t) 0x20) /* - An acceleration transient value greater than */ |

| #define | MMA865x_INT_SOURCE_SRC_TRANS_INACTIVE ((uint8_t) 0x00) /* - No transient event has occurred. */ |

| #define | MMA865x_INT_SOURCE_SRC_LNDPRT_READY ((uint8_t) 0x10) /* - An interrupt was generated due to a change in */ |

| #define | MMA865x_INT_SOURCE_SRC_LNDPRT_INACTIVE ((uint8_t) 0x00) /* - No change in orientation status was detected. */ |

| #define | MMA865x_INT_SOURCE_SRC_PULSE_READY ((uint8_t) 0x08) /* - An interrupt was generated due to single and/or */ |

| #define | MMA865x_INT_SOURCE_SRC_PULSE_INACTIVE ((uint8_t) 0x00) /* - No pulse event was detected. */ |

| #define | MMA865x_INT_SOURCE_SRC_FF_MT_READY ((uint8_t) 0x04) /* - The Freefall/Motion function interrupt is */ |

| #define | MMA865x_INT_SOURCE_SRC_FF_MT_INACTIVE ((uint8_t) 0x00) /* - No Freefall or Motion event was detected. */ |

| #define | MMA865x_INT_SOURCE_SRC_DRDY_READY ((uint8_t) 0x01) /* - The X, Y, Z data ready interrupt is active. */ |

| #define | MMA865x_INT_SOURCE_SRC_DRDY_INACTIVE ((uint8_t) 0x00) /* - The X, Y, Z interrupt is not active. */ |

| #define | MMA865x_XYZ_DATA_CFG_FS_MASK ((uint8_t) 0x03) |

| #define | MMA865x_XYZ_DATA_CFG_FS_SHIFT ((uint8_t) 0) |

| #define | MMA865x_XYZ_DATA_CFG_HPF_OUT_MASK ((uint8_t) 0x10) |

| #define | MMA865x_XYZ_DATA_CFG_HPF_OUT_SHIFT ((uint8_t) 4) |

| #define | MMA865x_XYZ_DATA_CFG_HPF_OUT_ENABLE ((uint8_t) 0x10) /* - Output data is high-pass filtered. */ |

| #define | MMA865x_XYZ_DATA_CFG_HPF_OUT_DISABLE ((uint8_t) 0x00) /* - Output data is not high-pass filtered. */ |

| #define | MMA865x_XYZ_DATA_CFG_FS_2G ((uint8_t) 0x00) /* - �2 g. */ |

| #define | MMA865x_XYZ_DATA_CFG_FS_4G ((uint8_t) 0x01) /* - �4 g. */ |

| #define | MMA865x_XYZ_DATA_CFG_FS_8G ((uint8_t) 0x02) /* - �8 g. */ |

| #define | MMA865x_HP_FILTER_CUTOFF_SEL_MASK ((uint8_t) 0x03) |

| #define | MMA865x_HP_FILTER_CUTOFF_SEL_SHIFT ((uint8_t) 0) |

| #define | MMA865x_HP_FILTER_CUTOFF_PULSE_LPF_EN_MASK ((uint8_t) 0x10) |

| #define | MMA865x_HP_FILTER_CUTOFF_PULSE_LPF_EN_SHIFT ((uint8_t) 4) |

| #define | MMA865x_HP_FILTER_CUTOFF_PULSE_HPF_BYP_MASK ((uint8_t) 0x20) |

| #define | MMA865x_HP_FILTER_CUTOFF_PULSE_HPF_BYP_SHIFT ((uint8_t) 5) |

| #define | MMA865x_HP_FILTER_CUTOFF_PULSE_HPF_BYP_ENABLED ((uint8_t) 0x00) /* - HPF is enabled for pulse processing. */ |

| #define | MMA865x_HP_FILTER_CUTOFF_PULSE_HPF_BYP_BYPASSED ((uint8_t) 0x20) /* - HPF is bypassed for pulse processing. */ |

| #define | MMA865x_HP_FILTER_CUTOFF_PULSE_LPF_EN_DISABLED ((uint8_t) 0x00) /* - LPF is disabled for pulse processing. */ |

| #define | MMA865x_HP_FILTER_CUTOFF_PULSE_LPF_EN_ENABLED ((uint8_t) 0x10) /* - LPF is enabled for pulse processing. */ |

| #define | MMA865x_HP_FILTER_CUTOFF_SEL_VAL_0 ((uint8_t) 0x00) /* - Select 0 0 */ |

| #define | MMA865x_HP_FILTER_CUTOFF_SEL_VAL_1 ((uint8_t) 0x00) /* - Select 0 1 */ |

| #define | MMA865x_HP_FILTER_CUTOFF_SEL_VAL_2 ((uint8_t) 0x00) /* - Select 1 0 */ |

| #define | MMA865x_HP_FILTER_CUTOFF_SEL_VAL_3 ((uint8_t) 0x00) /* - Select 1 1 */ |

| #define | MMA865x_PL_STATUS_BAFRO_MASK ((uint8_t) 0x01) |

| #define | MMA865x_PL_STATUS_BAFRO_SHIFT ((uint8_t) 0) |

| #define | MMA865x_PL_STATUS_LAPO_MASK ((uint8_t) 0x06) |

| #define | MMA865x_PL_STATUS_LAPO_SHIFT ((uint8_t) 1) |

| #define | MMA865x_PL_STATUS_LO_MASK ((uint8_t) 0x40) |

| #define | MMA865x_PL_STATUS_LO_SHIFT ((uint8_t) 6) |

| #define | MMA865x_PL_STATUS_NEWLP_MASK ((uint8_t) 0x80) |

| #define | MMA865x_PL_STATUS_NEWLP_SHIFT ((uint8_t) 7) |

| #define | MMA865x_PL_STATUS_NEWLP_NO_CHANGE ((uint8_t) 0x00) /* - No change. */ |

| #define | MMA865x_PL_STATUS_NEWLP_DETECTED ((uint8_t) 0x80) /* - BAFRO and/or LAPO and/or Z-Tilt lockout value has */ |

| #define | MMA865x_PL_STATUS_LO_NOT_DETECTED ((uint8_t) 0x00) /* - Lockout condition has not been detected. */ |

| #define | MMA865x_PL_STATUS_LO_DETECTED ((uint8_t) 0x40) /* - Z-Tilt lockout trip angle has been exceeded. */ |

| #define | MMA865x_PL_STATUS_LAPO_PORTRAIT_UP ((uint8_t) 0x00) /* - Portrait Up: Equipment standing vertically in the */ |

| #define | MMA865x_PL_STATUS_LAPO_PORTRAIT_DOWN ((uint8_t) 0x02) /* - Portrait Down: Equipment standing vertically in */ |

| #define | MMA865x_PL_STATUS_LAPO_LANDSCAPE_UP ((uint8_t) 0x04) /* - Landscape Right: Equipment is in landscape mode */ |

| #define | MMA865x_PL_STATUS_LAPO_LANDSCAPE_DOWN ((uint8_t) 0x06) /* - Landscape Left: Equipment is in landscape mode to */ |

| #define | MMA865x_PL_STATUS_BAFRO_FRONT ((uint8_t) 0x00) /* - Front: Equipment is in the front-facing */ |

| #define | MMA865x_PL_STATUS_BAFRO_BACK ((uint8_t) 0x01) /* - Back: Equipment is in the back-facing */ |

| #define | MMA865x_PL_CFG_PL_EN_MASK ((uint8_t) 0x40) |

| #define | MMA865x_PL_CFG_PL_EN_SHIFT ((uint8_t) 6) |

| #define | MMA865x_PL_CFG_DBCNTM_MASK ((uint8_t) 0x80) |

| #define | MMA865x_PL_CFG_DBCNTM_SHIFT ((uint8_t) 7) |

| #define | MMA865x_PL_CFG_DBCNTM_DECREMENT ((uint8_t) 0x00) /* - Decrements debounce whenever the condition of */ |

| #define | MMA865x_PL_CFG_DBCNTM_CLEAR ((uint8_t) 0x80) /* - Clears the counter whenever the condition of */ |

| #define | MMA865x_PL_CFG_PL_EN_DISABLED ((uint8_t) 0x00) /* - Portrait/Landscape Detection is disabled. */ |

| #define | MMA865x_PL_CFG_PL_EN_EN ((uint8_t) 0x40) /* - Portrait/Landscape Detection is enabled. */ |

| #define | MMA865x_PL_BF_ZCOMP_ZLOCK_MASK ((uint8_t) 0x07) |

| #define | MMA865x_PL_BF_ZCOMP_ZLOCK_SHIFT ((uint8_t) 0) |

| #define | MMA865x_PL_BF_ZCOMP_BKFR_MASK ((uint8_t) 0xC0) |

| #define | MMA865x_PL_BF_ZCOMP_BKFR_SHIFT ((uint8_t) 6) |

| #define | MMA865x_PL_BF_ZCOMP_BKFR_VAL_0 ((uint8_t) 0x00) /* - Back/Front Transition : 00 Z < 80� or Z > 280� */ |

| #define | MMA865x_PL_BF_ZCOMP_BKFR_VAL_1 ((uint8_t) 0x40) /* - Back/Front Transition : 01 Z < 75� or Z > 285� */ |

| #define | MMA865x_PL_BF_ZCOMP_BKFR_VAL_2 ((uint8_t) 0x80) /* - Back/Front Transition : 10 Z < 70� or Z > 290� */ |

| #define | MMA865x_PL_BF_ZCOMP_BKFR_VAL_3 ((uint8_t) 0xc0) /* - Back/Front Transition : 11 Z < 65� or Z > 295� */ |

| #define | MMA865x_PL_BF_ZCOMP_ZLOCK_VAL_14 ((uint8_t) 0x00) /* - Threshold Angle = 14�. */ |

| #define | MMA865x_PL_BF_ZCOMP_ZLOCK_VAL_18 ((uint8_t) 0x01) /* - Threshold Angle = 18�. */ |

| #define | MMA865x_PL_BF_ZCOMP_ZLOCK_VAL_21 ((uint8_t) 0x02) /* - Threshold Angle = 21�. */ |

| #define | MMA865x_PL_BF_ZCOMP_ZLOCK_VAL_25 ((uint8_t) 0x03) /* - Threshold Angle = 25�. */ |

| #define | MMA865x_PL_BF_ZCOMP_ZLOCK_VAL_29 ((uint8_t) 0x04) /* - Threshold Angle = 29�. */ |

| #define | MMA865x_PL_BF_ZCOMP_ZLOCK_VAL_33 ((uint8_t) 0x05) /* - Threshold Angle = 33�. */ |

| #define | MMA865x_PL_BF_ZCOMP_ZLOCK_VAL_37 ((uint8_t) 0x06) /* - Threshold Angle = 37�. */ |

| #define | MMA865x_PL_BF_ZCOMP_ZLOCK_VAL_42 ((uint8_t) 0x07) /* - Threshold Angle = 42�. */ |

| #define | MMA865x_P_L_THS_REG_HYS_MASK ((uint8_t) 0x07) |

| #define | MMA865x_P_L_THS_REG_HYS_SHIFT ((uint8_t) 0) |

| #define | MMA865x_P_L_THS_REG_P_L_THS_MASK ((uint8_t) 0xF8) |

| #define | MMA865x_P_L_THS_REG_P_L_THS_SHIFT ((uint8_t) 3) |

| #define | MMA865x_P_L_THS_REG_P_L_THS_VAL_15 ((uint8_t) 0x38) /* - Threshold Angle = 15� */ |

| #define | MMA865x_P_L_THS_REG_P_L_THS_VAL_20 ((uint8_t) 0x48) /* - Threshold Angle = 20� */ |

| #define | MMA865x_P_L_THS_REG_P_L_THS_VAL_30 ((uint8_t) 0x60) /* - Threshold Angle = 30� */ |

| #define | MMA865x_P_L_THS_REG_P_L_THS_VAL_35 ((uint8_t) 0x68) /* - Threshold Angle = 35� */ |

| #define | MMA865x_P_L_THS_REG_P_L_THS_VAL_40 ((uint8_t) 0x78) /* - Threshold Angle = 40� */ |

| #define | MMA865x_P_L_THS_REG_P_L_THS_VAL_45 ((uint8_t) 0x80) /* - Threshold Angle = 45� */ |

| #define | MMA865x_P_L_THS_REG_P_L_THS_VAL_55 ((uint8_t) 0x98) /* - Threshold Angle = 55� */ |

| #define | MMA865x_P_L_THS_REG_P_L_THS_VAL_60 ((uint8_t) 0xa0) /* - Threshold Angle = 60� */ |

| #define | MMA865x_P_L_THS_REG_P_L_THS_VAL_70 ((uint8_t) 0xb8) /* - Threshold Angle = 70� */ |

| #define | MMA865x_P_L_THS_REG_P_L_THS_VAL_75 ((uint8_t) 0xc8) /* - Threshold Angle = 75� */ |

| #define | MMA865x_P_L_THS_REG_HYS_VAL_0 ((uint8_t) 0x00) /* - Hysteresis � Angle Range = �0 */ |

| #define | MMA865x_P_L_THS_REG_HYS_VAL_1 ((uint8_t) 0x01) /* - Hysteresis � Angle Range = �4 */ |

| #define | MMA865x_P_L_THS_REG_HYS_VAL_2 ((uint8_t) 0x02) /* - Hysteresis � Angle Range = �7 */ |

| #define | MMA865x_P_L_THS_REG_HYS_VAL_3 ((uint8_t) 0x03) /* - Hysteresis � Angle Range = �11 */ |

| #define | MMA865x_P_L_THS_REG_HYS_VAL_4 ((uint8_t) 0x04) /* - Hysteresis � Angle Range = �14 */ |

| #define | MMA865x_P_L_THS_REG_HYS_VAL_5 ((uint8_t) 0x05) /* - Hysteresis � Angle Range = �17 */ |

| #define | MMA865x_P_L_THS_REG_HYS_VAL_6 ((uint8_t) 0x06) /* - Hysteresis � Angle Range = �21 */ |

| #define | MMA865x_P_L_THS_REG_HYS_VAL_7 ((uint8_t) 0x07) /* - Hysteresis � Angle Range = �24 */ |

| #define | MMA865x_FF_MT_CFG_XEFE_MASK ((uint8_t) 0x08) |

| #define | MMA865x_FF_MT_CFG_XEFE_SHIFT ((uint8_t) 3) |

| #define | MMA865x_FF_MT_CFG_YEFE_MASK ((uint8_t) 0x10) |

| #define | MMA865x_FF_MT_CFG_YEFE_SHIFT ((uint8_t) 4) |

| #define | MMA865x_FF_MT_CFG_ZEFE_MASK ((uint8_t) 0x20) |

| #define | MMA865x_FF_MT_CFG_ZEFE_SHIFT ((uint8_t) 5) |

| #define | MMA865x_FF_MT_CFG_OAE_MASK ((uint8_t) 0x40) |

| #define | MMA865x_FF_MT_CFG_OAE_SHIFT ((uint8_t) 6) |

| #define | MMA865x_FF_MT_CFG_ELE_MASK ((uint8_t) 0x80) |

| #define | MMA865x_FF_MT_CFG_ELE_SHIFT ((uint8_t) 7) |

| #define | MMA865x_FF_MT_CFG_ELE_DISABLED ((uint8_t) 0x00) /* - Event flag latch disabled. */ |

| #define | MMA865x_FF_MT_CFG_ELE_EN ((uint8_t) 0x80) /* - Event flag latch enabled. */ |

| #define | MMA865x_FF_MT_CFG_OAE_FREEFALL ((uint8_t) 0x00) /* - Freefall flag (Logical AND combination). */ |

| #define | MMA865x_FF_MT_CFG_OAE_MOTION ((uint8_t) 0x40) /* - Motion flag (Logical OR combination). */ |

| #define | MMA865x_FF_MT_CFG_ZEFE_DISABLED ((uint8_t) 0x00) /* - Event detection disabled. */ |

| #define | MMA865x_FF_MT_CFG_ZEFE_EN ((uint8_t) 0x20) /* - Raise event flag on measured acceleration value */ |

| #define | MMA865x_FF_MT_CFG_YEFE_DISABLED ((uint8_t) 0x00) /* - Event detection disabled. */ |

| #define | MMA865x_FF_MT_CFG_YEFE_EN ((uint8_t) 0x10) /* - Raise event flag on measured acceleration value */ |

| #define | MMA865x_FF_MT_CFG_XEFE_DISABLED ((uint8_t) 0x00) /* - Event detection disabled. */ |

| #define | MMA865x_FF_MT_CFG_XEFE_EN ((uint8_t) 0x08) /* - Raise event flag on measured acceleration value */ |

| #define | MMA865x_FF_MT_SRC_XHP_MASK ((uint8_t) 0x01) |

| #define | MMA865x_FF_MT_SRC_XHP_SHIFT ((uint8_t) 0) |

| #define | MMA865x_FF_MT_SRC_XHE_MASK ((uint8_t) 0x02) |

| #define | MMA865x_FF_MT_SRC_XHE_SHIFT ((uint8_t) 1) |

| #define | MMA865x_FF_MT_SRC_YHP_MASK ((uint8_t) 0x04) |

| #define | MMA865x_FF_MT_SRC_YHP_SHIFT ((uint8_t) 2) |

| #define | MMA865x_FF_MT_SRC_YHE_MASK ((uint8_t) 0x08) |

| #define | MMA865x_FF_MT_SRC_YHE_SHIFT ((uint8_t) 3) |

| #define | MMA865x_FF_MT_SRC_ZHP_MASK ((uint8_t) 0x10) |

| #define | MMA865x_FF_MT_SRC_ZHP_SHIFT ((uint8_t) 4) |

| #define | MMA865x_FF_MT_SRC_ZHE_MASK ((uint8_t) 0x20) |

| #define | MMA865x_FF_MT_SRC_ZHE_SHIFT ((uint8_t) 5) |

| #define | MMA865x_FF_MT_SRC_EA_MASK ((uint8_t) 0x80) |

| #define | MMA865x_FF_MT_SRC_EA_SHIFT ((uint8_t) 7) |

| #define | MMA865x_FF_MT_SRC_EA_NONE ((uint8_t) 0x00) /* - No event flag has been asserted. */ |

| #define | MMA865x_FF_MT_SRC_EA_DETECTED ((uint8_t) 0x80) /* - One or more event flags has been asserted. */ |

| #define | MMA865x_FF_MT_SRC_ZHE_NONE ((uint8_t) 0x00) /* - No Z motion event detected. */ |

| #define | MMA865x_FF_MT_SRC_ZHE_DETECTED ((uint8_t) 0x20) /* - Z motion has been detected. */ |

| #define | MMA865x_FF_MT_SRC_ZHP_POSITIVE ((uint8_t) 0x00) /* - Z event was positive g. */ |

| #define | MMA865x_FF_MT_SRC_ZHP_NEGATIVE ((uint8_t) 0x10) /* - Z event was negative g. */ |

| #define | MMA865x_FF_MT_SRC_YHE_NONE ((uint8_t) 0x00) /* - No Y motion event detected. */ |

| #define | MMA865x_FF_MT_SRC_YHE_DETECTED ((uint8_t) 0x08) /* - Y motion has been detected. */ |

| #define | MMA865x_FF_MT_SRC_YHP_POSITIVE ((uint8_t) 0x00) /* - Y event detected was positive g. */ |

| #define | MMA865x_FF_MT_SRC_YHP_NEGATIVE ((uint8_t) 0x04) /* - Y event was negative g. */ |

| #define | MMA865x_FF_MT_SRC_XHE_NONE ((uint8_t) 0x00) /* - No X motion event detected. */ |

| #define | MMA865x_FF_MT_SRC_XHE_DETECTED ((uint8_t) 0x02) /* - X motion has been detected. */ |

| #define | MMA865x_FF_MT_SRC_XHP_POSITIVE ((uint8_t) 0x00) /* - X event was positive g. */ |

| #define | MMA865x_FF_MT_SRC_XHP_NEGATIVE ((uint8_t) 0x01) /* - X event was negative g. */ |

| #define | MMA865x_FF_MT_THS_THS_MASK ((uint8_t) 0x7F) |

| #define | MMA865x_FF_MT_THS_THS_SHIFT ((uint8_t) 0) |

| #define | MMA865x_FF_MT_THS_DBCNTM_MASK ((uint8_t) 0x80) |

| #define | MMA865x_FF_MT_THS_DBCNTM_SHIFT ((uint8_t) 7) |

| #define | MMA865x_FF_MT_THS_DBCNTM_INC_DEC ((uint8_t) 0x00) /* - Increments or decrements debounce. */ |

| #define | MMA865x_FF_MT_THS_DBCNTM_INC_CLR ((uint8_t) 0x80) /* - Increments or clears counter. */ |

| #define | MMA865x_TRANSIENT_CFG_HPF_BYP_MASK ((uint8_t) 0x01) |

| #define | MMA865x_TRANSIENT_CFG_HPF_BYP_SHIFT ((uint8_t) 0) |

| #define | MMA865x_TRANSIENT_CFG_XTEFE_MASK ((uint8_t) 0x02) |

| #define | MMA865x_TRANSIENT_CFG_XTEFE_SHIFT ((uint8_t) 1) |

| #define | MMA865x_TRANSIENT_CFG_YTEFE_MASK ((uint8_t) 0x04) |

| #define | MMA865x_TRANSIENT_CFG_YTEFE_SHIFT ((uint8_t) 2) |

| #define | MMA865x_TRANSIENT_CFG_ZTEFE_MASK ((uint8_t) 0x08) |

| #define | MMA865x_TRANSIENT_CFG_ZTEFE_SHIFT ((uint8_t) 3) |

| #define | MMA865x_TRANSIENT_CFG_ELE_MASK ((uint8_t) 0x10) |

| #define | MMA865x_TRANSIENT_CFG_ELE_SHIFT ((uint8_t) 4) |

| #define | MMA865x_TRANSIENT_CFG_ELE_DISABLED ((uint8_t) 0x00) /* - Event flag latch disabled. */ |

| #define | MMA865x_TRANSIENT_CFG_ELE_EN ((uint8_t) 0x10) /* - Event flag latch enabled. */ |

| #define | MMA865x_TRANSIENT_CFG_ZTEFE_DISABLED ((uint8_t) 0x00) /* - Event detection disabled. */ |

| #define | MMA865x_TRANSIENT_CFG_ZTEFE_EN ((uint8_t) 0x08) /* - Raise event flag on measured acceleration */ |

| #define | MMA865x_TRANSIENT_CFG_YTEFE_DISABLED ((uint8_t) 0x00) /* - Event detection disabled. */ |

| #define | MMA865x_TRANSIENT_CFG_YTEFE_EN ((uint8_t) 0x04) /* - Raise event flag on measured acceleration */ |

| #define | MMA865x_TRANSIENT_CFG_XTEFE_DISABLED ((uint8_t) 0x00) /* - Event detection disabled. */ |

| #define | MMA865x_TRANSIENT_CFG_XTEFE_EN ((uint8_t) 0x02) /* - Raise event flag on measured acceleration */ |

| #define | MMA865x_TRANSIENT_CFG_HPF_BYP_THROUGH_HPF ((uint8_t) 0x00) /* - Data to transient acceleration detection */ |

| #define | MMA865x_TRANSIENT_CFG_HPF_BYP_NOT_HPF ((uint8_t) 0x01) /* - Data to transient acceleration detection */ |

| #define | MMA865x_TRANSIENT_SRC_X_TRANS_POL_MASK ((uint8_t) 0x01) |

| #define | MMA865x_TRANSIENT_SRC_X_TRANS_POL_SHIFT ((uint8_t) 0) |

| #define | MMA865x_TRANSIENT_SRC_XTRANSE_MASK ((uint8_t) 0x02) |

| #define | MMA865x_TRANSIENT_SRC_XTRANSE_SHIFT ((uint8_t) 1) |

| #define | MMA865x_TRANSIENT_SRC_Y_TRANS_POL_MASK ((uint8_t) 0x04) |

| #define | MMA865x_TRANSIENT_SRC_Y_TRANS_POL_SHIFT ((uint8_t) 2) |

| #define | MMA865x_TRANSIENT_SRC_YTRANSE_MASK ((uint8_t) 0x08) |

| #define | MMA865x_TRANSIENT_SRC_YTRANSE_SHIFT ((uint8_t) 3) |

| #define | MMA865x_TRANSIENT_SRC_Z_TRANS_POL_MASK ((uint8_t) 0x10) |

| #define | MMA865x_TRANSIENT_SRC_Z_TRANS_POL_SHIFT ((uint8_t) 4) |

| #define | MMA865x_TRANSIENT_SRC_ZTRANSE_MASK ((uint8_t) 0x20) |

| #define | MMA865x_TRANSIENT_SRC_ZTRANSE_SHIFT ((uint8_t) 5) |

| #define | MMA865x_TRANSIENT_SRC_EA_MASK ((uint8_t) 0x40) |

| #define | MMA865x_TRANSIENT_SRC_EA_SHIFT ((uint8_t) 6) |

| #define | MMA865x_TRANSIENT_SRC_EA_NONE ((uint8_t) 0x00) /* - No event flag has been asserted. */ |

| #define | MMA865x_TRANSIENT_SRC_EA_DETECTED ((uint8_t) 0x40) /* - One or more event flags has been asserted. */ |

| #define | MMA865x_TRANSIENT_SRC_ZTRANSE_NONE ((uint8_t) 0x00) /* - No interrupt. */ |

| #define | MMA865x_TRANSIENT_SRC_ZTRANSE_DETECTED ((uint8_t) 0x20) /* - Z-transient acceleration greater than the */ |

| #define | MMA865x_TRANSIENT_SRC_Z_TRANS_POL_POSITIVE ((uint8_t) 0x00) /* - Z-event was positive g. */ |

| #define | MMA865x_TRANSIENT_SRC_Z_TRANS_POL_NEGATIVE ((uint8_t) 0x10) /* - Z-event was negative g. */ |

| #define | MMA865x_TRANSIENT_SRC_YTRANSE_NONE ((uint8_t) 0x00) /* - No interrupt. */ |

| #define | MMA865x_TRANSIENT_SRC_YTRANSE_DETECTED ((uint8_t) 0x08) /* - Y-transient acceleration greater than the */ |

| #define | MMA865x_TRANSIENT_SRC_Y_TRANS_POL_POSITIVE ((uint8_t) 0x00) /* - Y-event was Positive g. */ |

| #define | MMA865x_TRANSIENT_SRC_Y_TRANS_POL_NEGATIVE ((uint8_t) 0x04) /* - Y-event was Negative g. */ |

| #define | MMA865x_TRANSIENT_SRC_XTRANSE_NONE ((uint8_t) 0x00) /* - No interrupt. */ |

| #define | MMA865x_TRANSIENT_SRC_XTRANSE_DETECTED ((uint8_t) 0x02) /* - X-transient acceleration greater than the */ |

| #define | MMA865x_TRANSIENT_SRC_X_TRANS_POL_POSITIVE ((uint8_t) 0x00) /* - X-event was Positive g. */ |

| #define | MMA865x_TRANSIENT_SRC_X_TRANS_POL_NEGATIVE ((uint8_t) 0x01) /* - X-event was Negative g. */ |

| #define | MMA865x_TRANSIENT_THS_THS_MASK ((uint8_t) 0x7F) |

| #define | MMA865x_TRANSIENT_THS_THS_SHIFT ((uint8_t) 0) |

| #define | MMA865x_TRANSIENT_THS_DBCNTM_MASK ((uint8_t) 0x80) |

| #define | MMA865x_TRANSIENT_THS_DBCNTM_SHIFT ((uint8_t) 7) |

| #define | MMA865x_TRANSIENT_THS_DBCNTM_INC_DEC ((uint8_t) 0x00) /* - Increments or decrements debounce. */ |

| #define | MMA865x_TRANSIENT_THS_DBCNTM_INC_CLR ((uint8_t) 0x80) /* - Increments or clears counter. */ |

| #define | MMA865x_PULSE_CFG_XSPEFE_MASK ((uint8_t) 0x01) |

| #define | MMA865x_PULSE_CFG_XSPEFE_SHIFT ((uint8_t) 0) |

| #define | MMA865x_PULSE_CFG_XDPEFE_MASK ((uint8_t) 0x02) |

| #define | MMA865x_PULSE_CFG_XDPEFE_SHIFT ((uint8_t) 1) |

| #define | MMA865x_PULSE_CFG_YSPEFE_MASK ((uint8_t) 0x04) |

| #define | MMA865x_PULSE_CFG_YSPEFE_SHIFT ((uint8_t) 2) |

| #define | MMA865x_PULSE_CFG_YDPEFE_MASK ((uint8_t) 0x08) |

| #define | MMA865x_PULSE_CFG_YDPEFE_SHIFT ((uint8_t) 3) |

| #define | MMA865x_PULSE_CFG_ZSPEFE_MASK ((uint8_t) 0x10) |

| #define | MMA865x_PULSE_CFG_ZSPEFE_SHIFT ((uint8_t) 4) |

| #define | MMA865x_PULSE_CFG_ZDPEFE_MASK ((uint8_t) 0x20) |

| #define | MMA865x_PULSE_CFG_ZDPEFE_SHIFT ((uint8_t) 5) |

| #define | MMA865x_PULSE_CFG_ELE_MASK ((uint8_t) 0x40) |

| #define | MMA865x_PULSE_CFG_ELE_SHIFT ((uint8_t) 6) |

| #define | MMA865x_PULSE_CFG_DPA_MASK ((uint8_t) 0x80) |

| #define | MMA865x_PULSE_CFG_DPA_SHIFT ((uint8_t) 7) |

| #define | MMA865x_PULSE_CFG_DPA_NOT_ABORTED ((uint8_t) 0x00) /* - Double Pulse detection is not aborted if the */ |

| #define | MMA865x_PULSE_CFG_DPA_SUSPENDED ((uint8_t) 0x80) /* - Setting the DPA bit momentarily suspends the */ |

| #define | MMA865x_PULSE_CFG_ELE_DISABLED ((uint8_t) 0x00) /* - Event detection is disabled. */ |

| #define | MMA865x_PULSE_CFG_ELE_EN ((uint8_t) 0x40) /* - Event detection is enabled. */ |

| #define | MMA865x_PULSE_CFG_ZDPEFE_DISABLED ((uint8_t) 0x00) /* - Event detection is disabled. */ |

| #define | MMA865x_PULSE_CFG_ZDPEFE_EN ((uint8_t) 0x20) /* - Event detection is enabled. */ |

| #define | MMA865x_PULSE_CFG_ZSPEFE_DISABLED ((uint8_t) 0x00) /* - Event detection is disabled. */ |

| #define | MMA865x_PULSE_CFG_ZSPEFE_EN ((uint8_t) 0x10) /* - Event detection is enabled. */ |

| #define | MMA865x_PULSE_CFG_YDPEFE_DISABLED ((uint8_t) 0x00) /* - Event detection is disabled. */ |

| #define | MMA865x_PULSE_CFG_YDPEFE_EN ((uint8_t) 0x08) /* - Event detection is enabled. */ |

| #define | MMA865x_PULSE_CFG_YSPEFE_DISABLED ((uint8_t) 0x00) /* - Event detection is disabled. */ |

| #define | MMA865x_PULSE_CFG_YSPEFE_EN ((uint8_t) 0x04) /* - Event detection is enabled. */ |

| #define | MMA865x_PULSE_CFG_XDPEFE_DISABLED ((uint8_t) 0x00) /* - Event detection is disabled. */ |

| #define | MMA865x_PULSE_CFG_XDPEFE_EN ((uint8_t) 0x02) /* - Event detection is enabled. */ |

| #define | MMA865x_PULSE_CFG_XSPEFE_DISABLED ((uint8_t) 0x00) /* - Event detection is disabled. */ |

| #define | MMA865x_PULSE_CFG_XSPEFE_EN ((uint8_t) 0x01) /* - Event detection is enabled. */ |

| #define | MMA865x_PULSE_SRC_POL_X_MASK ((uint8_t) 0x01) |

| #define | MMA865x_PULSE_SRC_POL_X_SHIFT ((uint8_t) 0) |

| #define | MMA865x_PULSE_SRC_POL_Y_MASK ((uint8_t) 0x02) |

| #define | MMA865x_PULSE_SRC_POL_Y_SHIFT ((uint8_t) 1) |

| #define | MMA865x_PULSE_SRC_POL_Z_MASK ((uint8_t) 0x04) |

| #define | MMA865x_PULSE_SRC_POL_Z_SHIFT ((uint8_t) 2) |

| #define | MMA865x_PULSE_SRC_DPE_MASK ((uint8_t) 0x08) |

| #define | MMA865x_PULSE_SRC_DPE_SHIFT ((uint8_t) 3) |

| #define | MMA865x_PULSE_SRC_AXX_MASK ((uint8_t) 0x10) |

| #define | MMA865x_PULSE_SRC_AXX_SHIFT ((uint8_t) 4) |

| #define | MMA865x_PULSE_SRC_AXY_MASK ((uint8_t) 0x20) |

| #define | MMA865x_PULSE_SRC_AXY_SHIFT ((uint8_t) 5) |

| #define | MMA865x_PULSE_SRC_AXZ_MASK ((uint8_t) 0x40) |

| #define | MMA865x_PULSE_SRC_AXZ_SHIFT ((uint8_t) 6) |

| #define | MMA865x_PULSE_SRC_EA_MASK ((uint8_t) 0x80) |

| #define | MMA865x_PULSE_SRC_EA_SHIFT ((uint8_t) 7) |

| #define | MMA865x_PULSE_SRC_EA_NONE ((uint8_t) 0x00) /* - No interrupt has been generated. */ |

| #define | MMA865x_PULSE_SRC_EA_DETECTED ((uint8_t) 0x80) /* - One or more interrupt events have been generated. */ |

| #define | MMA865x_PULSE_SRC_AXZ_NONE ((uint8_t) 0x00) /* - No interrupt. */ |

| #define | MMA865x_PULSE_SRC_AXZ_DETECTED ((uint8_t) 0x40) /* - Z-axis event has occurred. */ |

| #define | MMA865x_PULSE_SRC_AXY_NONE ((uint8_t) 0x00) /* - No interrupt. */ |

| #define | MMA865x_PULSE_SRC_AXY_DETECTED ((uint8_t) 0x20) /* - Y-axis event has occurred. */ |

| #define | MMA865x_PULSE_SRC_AXX_NONE ((uint8_t) 0x00) /* - No interrupt. */ |

| #define | MMA865x_PULSE_SRC_AXX_DETECTED ((uint8_t) 0x10) /* - X-axis event has occurred. */ |

| #define | MMA865x_PULSE_SRC_DPE_SINGLE ((uint8_t) 0x00) /* - Single pulse event triggered interrupt. */ |

| #define | MMA865x_PULSE_SRC_DPE_DOUBLE ((uint8_t) 0x08) /* - Double pulse event triggered interrupt. */ |

| #define | MMA865x_PULSE_SRC_POL_Z_POSITIVE ((uint8_t) 0x00) /* - Pulse event that triggered interrupt was */ |

| #define | MMA865x_PULSE_SRC_POL_Z_NEGATIVE ((uint8_t) 0x04) /* - Pulse event that triggered interrupt was */ |

| #define | MMA865x_PULSE_SRC_POL_Y_POSITIVE ((uint8_t) 0x00) /* - Pulse event that triggered interrupt was */ |

| #define | MMA865x_PULSE_SRC_POL_Y_NEGATIVE ((uint8_t) 0x02) /* - Pulse event that triggered interrupt was */ |

| #define | MMA865x_PULSE_SRC_POL_X_POSITIVE ((uint8_t) 0x00) /* - Pulse event that triggered interrupt was */ |

| #define | MMA865x_PULSE_SRC_POL_X_NEGATIVE ((uint8_t) 0x01) /* - Pulse event that triggered interrupt was */ |

| #define | MMA865x_PULSE_THSX_THSX_MASK ((uint8_t) 0x7F) |

| #define | MMA865x_PULSE_THSX_THSX_SHIFT ((uint8_t) 0) |

| #define | MMA865x_PULSE_THSY_THSY_MASK ((uint8_t) 0x7F) |

| #define | MMA865x_PULSE_THSY_THSY_SHIFT ((uint8_t) 0) |

| #define | MMA865x_PULSE_THSZ_THSZ_MASK ((uint8_t) 0x7F) |

| #define | MMA865x_PULSE_THSZ_THSZ_SHIFT ((uint8_t) 0) |

| #define | MMA865x_CTRL_REG1_ACTIVE_MASK ((uint8_t) 0x01) |

| #define | MMA865x_CTRL_REG1_ACTIVE_SHIFT ((uint8_t) 0) |

| #define | MMA865x_CTRL_REG1_F_READ_MASK ((uint8_t) 0x02) |

| #define | MMA865x_CTRL_REG1_F_READ_SHIFT ((uint8_t) 1) |

| #define | MMA865x_CTRL_REG1_DR_MASK ((uint8_t) 0x38) |

| #define | MMA865x_CTRL_REG1_DR_SHIFT ((uint8_t) 3) |

| #define | MMA865x_CTRL_REG1_ASLP_RATE_MASK ((uint8_t) 0xC0) |

| #define | MMA865x_CTRL_REG1_ASLP_RATE_SHIFT ((uint8_t) 6) |

| #define | MMA865x_CTRL_REG1_ASLP_RATE_50HZ ((uint8_t) 0x00) /* - Frequency = 50Hz */ |

| #define | MMA865x_CTRL_REG1_ASLP_RATE_12_5HZ ((uint8_t) 0x40) /* - Frequency = 12.5Hz */ |

| #define | MMA865x_CTRL_REG1_ASLP_RATE_6_25HZ ((uint8_t) 0x80) /* - Frequency = 6.25Hz */ |

| #define | MMA865x_CTRL_REG1_ASLP_RATE_1_56HZ ((uint8_t) 0xc0) /* - Frequency = 1.56Hz */ |

| #define | MMA865x_CTRL_REG1_DR_800HZ ((uint8_t) 0x00) /* - ODR = 800Hz. */ |

| #define | MMA865x_CTRL_REG1_DR_400HZ ((uint8_t) 0x08) /* - ODR = 400Hz. */ |

| #define | MMA865x_CTRL_REG1_DR_200HZ ((uint8_t) 0x10) /* - ODR = 200Hz. */ |

| #define | MMA865x_CTRL_REG1_DR_100HZ ((uint8_t) 0x18) /* - ODR = 100Hz. */ |

| #define | MMA865x_CTRL_REG1_DR_50HZ ((uint8_t) 0x20) /* - ODR = 50Hz. */ |

| #define | MMA865x_CTRL_REG1_DR_12_5HZ ((uint8_t) 0x28) /* - ODR = 12.5Hz. */ |

| #define | MMA865x_CTRL_REG1_DR_6_25HZ ((uint8_t) 0x30) /* - ODR = 6.25Hz. */ |

| #define | MMA865x_CTRL_REG1_DR_1_56HZ ((uint8_t) 0x38) /* - ODR = 1.56Hz. */ |

| #define | MMA865x_CTRL_REG1_F_READ_NORMAL ((uint8_t) 0x00) /* - Normal Mode. */ |

| #define | MMA865x_CTRL_REG1_F_READ_FAST ((uint8_t) 0x02) /* - Fast Read Mode. */ |

| #define | MMA865x_CTRL_REG1_ACTIVE_STANDBY ((uint8_t) 0x00) /* - STANDBY mode. */ |

| #define | MMA865x_CTRL_REG1_ACTIVE_ACTIVATED ((uint8_t) 0x01) /* - ACTIVE mode. */ |

| #define | MMA865x_CTRL_REG2_MODS_MASK ((uint8_t) 0x03) |

| #define | MMA865x_CTRL_REG2_MODS_SHIFT ((uint8_t) 0) |

| #define | MMA865x_CTRL_REG2_SLPE_MASK ((uint8_t) 0x04) |

| #define | MMA865x_CTRL_REG2_SLPE_SHIFT ((uint8_t) 2) |

| #define | MMA865x_CTRL_REG2_SMODS_MASK ((uint8_t) 0x18) |

| #define | MMA865x_CTRL_REG2_SMODS_SHIFT ((uint8_t) 3) |

| #define | MMA865x_CTRL_REG2_RST_MASK ((uint8_t) 0x40) |

| #define | MMA865x_CTRL_REG2_RST_SHIFT ((uint8_t) 6) |

| #define | MMA865x_CTRL_REG2_ST_MASK ((uint8_t) 0x80) |

| #define | MMA865x_CTRL_REG2_ST_SHIFT ((uint8_t) 7) |

| #define | MMA865x_CTRL_REG2_ST_DISABLED ((uint8_t) 0x00) /* - Self-Test disabled. */ |

| #define | MMA865x_CTRL_REG2_ST_EN ((uint8_t) 0x80) /* - Self-Test enabled. */ |

| #define | MMA865x_CTRL_REG2_RST_DISABLED ((uint8_t) 0x00) /* - Device reset disabled. */ |

| #define | MMA865x_CTRL_REG2_RST_EN ((uint8_t) 0x40) /* - Device reset enabled. */ |

| #define | MMA865x_CTRL_REG2_SMODS_NORMAL ((uint8_t) 0x00) /* - Normal Mode. */ |

| #define | MMA865x_CTRL_REG2_SMODS_LNLP ((uint8_t) 0x08) /* - Low Noise Low Power Mode. */ |

| #define | MMA865x_CTRL_REG2_SMODS_HR ((uint8_t) 0x10) /* - High Resolution Mode. */ |

| #define | MMA865x_CTRL_REG2_SMODS_LP ((uint8_t) 0x18) /* - Low Power Mode. */ |

| #define | MMA865x_CTRL_REG2_SLPE_DISABLED ((uint8_t) 0x00) /* - Auto-SLEEP is not enabled. */ |

| #define | MMA865x_CTRL_REG2_SLPE_EN ((uint8_t) 0x04) /* - Auto-SLEEP is enabled. */ |

| #define | MMA865x_CTRL_REG2_MODS_NORMAL ((uint8_t) 0x00) /* - Normal Mode. */ |

| #define | MMA865x_CTRL_REG2_MODS_LNLP ((uint8_t) 0x01) /* - Low Noise Low Power Mode. */ |

| #define | MMA865x_CTRL_REG2_MODS_HR ((uint8_t) 0x02) /* - High Resolution Mode. */ |

| #define | MMA865x_CTRL_REG2_MODS_LP ((uint8_t) 0x03) /* - Low Power Mode. */ |

| #define | MMA865x_CTRL_REG3_PP_OD_MASK ((uint8_t) 0x01) |

| #define | MMA865x_CTRL_REG3_PP_OD_SHIFT ((uint8_t) 0) |

| #define | MMA865x_CTRL_REG3_IPOL_MASK ((uint8_t) 0x02) |

| #define | MMA865x_CTRL_REG3_IPOL_SHIFT ((uint8_t) 1) |

| #define | MMA865x_CTRL_REG3_WAKE_FF_MT_MASK ((uint8_t) 0x08) |

| #define | MMA865x_CTRL_REG3_WAKE_FF_MT_SHIFT ((uint8_t) 3) |

| #define | MMA865x_CTRL_REG3_WAKE_PULSE_MASK ((uint8_t) 0x10) |

| #define | MMA865x_CTRL_REG3_WAKE_PULSE_SHIFT ((uint8_t) 4) |

| #define | MMA865x_CTRL_REG3_WAKE_LNDPRT_MASK ((uint8_t) 0x20) |

| #define | MMA865x_CTRL_REG3_WAKE_LNDPRT_SHIFT ((uint8_t) 5) |

| #define | MMA865x_CTRL_REG3_WAKE_TRANS_MASK ((uint8_t) 0x40) |

| #define | MMA865x_CTRL_REG3_WAKE_TRANS_SHIFT ((uint8_t) 6) |

| #define | MMA865x_CTRL_REG3_FIFO_GATE_MASK ((uint8_t) 0x80) |

| #define | MMA865x_CTRL_REG3_FIFO_GATE_SHIFT ((uint8_t) 7) |

| #define | MMA865x_CTRL_REG3_FIFO_GATE_BYPASSED ((uint8_t) 0x00) /* - FIFO gate is bypassed. */ |

| #define | MMA865x_CTRL_REG3_FIFO_GATE_BLOCKED ((uint8_t) 0x80) /* - The FIFO input buffer is blocked when */ |

| #define | MMA865x_CTRL_REG3_WAKE_TRANS_BYPASSED ((uint8_t) 0x00) /* - Transient function is bypassed in SLEEP mode. */ |

| #define | MMA865x_CTRL_REG3_WAKE_TRANS_EN ((uint8_t) 0x40) /* - Transient function interrupt can wake up system. */ |

| #define | MMA865x_CTRL_REG3_WAKE_LNDPRT_BYPASSED ((uint8_t) 0x00) /* - Orientation function is bypassed in SLEEP mode. */ |

| #define | MMA865x_CTRL_REG3_WAKE_LNDPRT_EN ((uint8_t) 0x20) /* - Orientation function interrupt can wake up */ |

| #define | MMA865x_CTRL_REG3_WAKE_PULSE_BYPASSED ((uint8_t) 0x00) /* - Pulse function is bypassed in SLEEP mode. */ |

| #define | MMA865x_CTRL_REG3_WAKE_PULSE_EN ((uint8_t) 0x10) /* - Pulse function interrupt can wake up system. */ |

| #define | MMA865x_CTRL_REG3_WAKE_FF_MT_BYPASSED ((uint8_t) 0x00) /* - Freefall/Motion function is bypassed in SLEEP */ |

| #define | MMA865x_CTRL_REG3_WAKE_FF_MT_EN ((uint8_t) 0x08) /* - Freefall/Motion function interrupt can wake up. */ |

| #define | MMA865x_CTRL_REG3_IPOL_ACTIVE_LOW ((uint8_t) 0x00) /* - ACTIVE low. */ |

| #define | MMA865x_CTRL_REG3_IPOL_ACTIVE_HIGH ((uint8_t) 0x02) /* - ACTIVE high. */ |

| #define | MMA865x_CTRL_REG3_PP_OD_PUSH_PULL ((uint8_t) 0x00) /* - Push-Pull. */ |

| #define | MMA865x_CTRL_REG3_PP_OD_OPEN_DRAIN ((uint8_t) 0x01) /* - Open Drain. */ |

| #define | MMA865x_CTRL_REG4_INT_EN_DRDY_MASK ((uint8_t) 0x01) |

| #define | MMA865x_CTRL_REG4_INT_EN_DRDY_SHIFT ((uint8_t) 0) |

| #define | MMA865x_CTRL_REG4_INT_EN_FF_MT_MASK ((uint8_t) 0x04) |

| #define | MMA865x_CTRL_REG4_INT_EN_FF_MT_SHIFT ((uint8_t) 2) |

| #define | MMA865x_CTRL_REG4_INT_EN_PULSE_MASK ((uint8_t) 0x08) |

| #define | MMA865x_CTRL_REG4_INT_EN_PULSE_SHIFT ((uint8_t) 3) |

| #define | MMA865x_CTRL_REG4_INT_EN_LNDPRT_MASK ((uint8_t) 0x10) |

| #define | MMA865x_CTRL_REG4_INT_EN_LNDPRT_SHIFT ((uint8_t) 4) |

| #define | MMA865x_CTRL_REG4_INT_EN_TRANS_MASK ((uint8_t) 0x20) |

| #define | MMA865x_CTRL_REG4_INT_EN_TRANS_SHIFT ((uint8_t) 5) |

| #define | MMA865x_CTRL_REG4_INT_EN_FIFO_MASK ((uint8_t) 0x40) |

| #define | MMA865x_CTRL_REG4_INT_EN_FIFO_SHIFT ((uint8_t) 6) |

| #define | MMA865x_CTRL_REG4_INT_EN_ASLP_MASK ((uint8_t) 0x80) |

| #define | MMA865x_CTRL_REG4_INT_EN_ASLP_SHIFT ((uint8_t) 7) |

| #define | MMA865x_CTRL_REG4_INT_EN_ASLP_DISABLED ((uint8_t) 0x00) /* - Interrupt is disabled. */ |

| #define | MMA865x_CTRL_REG4_INT_EN_ASLP_EN ((uint8_t) 0x80) /* - Interrupt is enabled. */ |

| #define | MMA865x_CTRL_REG4_INT_EN_FIFO_DISABLED ((uint8_t) 0x00) /* - Interrupt is disabled. */ |

| #define | MMA865x_CTRL_REG4_INT_EN_FIFO_EN ((uint8_t) 0x40) /* - Interrupt is enabled. */ |

| #define | MMA865x_CTRL_REG4_INT_EN_TRANS_DISABLED ((uint8_t) 0x00) /* - Interrupt is disabled. */ |

| #define | MMA865x_CTRL_REG4_INT_EN_TRANS_EN ((uint8_t) 0x20) /* - Interrupt is enabled. */ |

| #define | MMA865x_CTRL_REG4_INT_EN_LNDPRT_DISABLED ((uint8_t) 0x00) /* - Interrupt is disabled. */ |

| #define | MMA865x_CTRL_REG4_INT_EN_LNDPRT_EN ((uint8_t) 0x10) /* - Interrupt is enabled. */ |

| #define | MMA865x_CTRL_REG4_INT_EN_PULSE_DISABLED ((uint8_t) 0x00) /* - Interrupt is disabled. */ |

| #define | MMA865x_CTRL_REG4_INT_EN_PULSE_EN ((uint8_t) 0x08) /* - Interrupt is enabled. */ |

| #define | MMA865x_CTRL_REG4_INT_EN_FF_MT_DISABLED ((uint8_t) 0x00) /* - Interrupt is disabled. */ |

| #define | MMA865x_CTRL_REG4_INT_EN_FF_MT_EN ((uint8_t) 0x04) /* - Interrupt is enabled. */ |

| #define | MMA865x_CTRL_REG4_INT_EN_DRDY_DISABLED ((uint8_t) 0x00) /* - Interrupt is disabled. */ |

| #define | MMA865x_CTRL_REG4_INT_EN_DRDY_EN ((uint8_t) 0x01) /* - Interrupt is enabled. */ |

| #define | MMA865x_CTRL_REG5_INT_CFG_DRDY_MASK ((uint8_t) 0x01) |

| #define | MMA865x_CTRL_REG5_INT_CFG_DRDY_SHIFT ((uint8_t) 0) |

| #define | MMA865x_CTRL_REG5_INT_CFG_FF_MT_MASK ((uint8_t) 0x04) |

| #define | MMA865x_CTRL_REG5_INT_CFG_FF_MT_SHIFT ((uint8_t) 2) |

| #define | MMA865x_CTRL_REG5_INT_CFG_PULSE_MASK ((uint8_t) 0x08) |

| #define | MMA865x_CTRL_REG5_INT_CFG_PULSE_SHIFT ((uint8_t) 3) |

| #define | MMA865x_CTRL_REG5_INT_CFG_LNDPRT_MASK ((uint8_t) 0x10) |

| #define | MMA865x_CTRL_REG5_INT_CFG_LNDPRT_SHIFT ((uint8_t) 4) |

| #define | MMA865x_CTRL_REG5_INT_CFG_TRANS_MASK ((uint8_t) 0x20) |

| #define | MMA865x_CTRL_REG5_INT_CFG_TRANS_SHIFT ((uint8_t) 5) |

| #define | MMA865x_CTRL_REG5_INT_CFG_FIFO_MASK ((uint8_t) 0x40) |

| #define | MMA865x_CTRL_REG5_INT_CFG_FIFO_SHIFT ((uint8_t) 6) |

| #define | MMA865x_CTRL_REG5_INT_CFG_ASLP_MASK ((uint8_t) 0x80) |

| #define | MMA865x_CTRL_REG5_INT_CFG_ASLP_SHIFT ((uint8_t) 7) |

| #define | MMA865x_CTRL_REG5_INT_CFG_ASLP_INT2 ((uint8_t) 0x00) /* - Interrupt is routed to INT2 pin. */ |

| #define | MMA865x_CTRL_REG5_INT_CFG_ASLP_INT1 ((uint8_t) 0x80) /* - Interrupt is routed to INT1 pin. */ |

| #define | MMA865x_CTRL_REG5_INT_CFG_FIFO_INT2 ((uint8_t) 0x00) /* - Interrupt is routed to INT2 pin. */ |

| #define | MMA865x_CTRL_REG5_INT_CFG_FIFO_INT1 ((uint8_t) 0x40) /* - Interrupt is routed to INT1 pin. */ |

| #define | MMA865x_CTRL_REG5_INT_CFG_TRANS_INT2 ((uint8_t) 0x00) /* - Interrupt is routed to INT2 pin. */ |

| #define | MMA865x_CTRL_REG5_INT_CFG_TRANS_INT1 ((uint8_t) 0x20) /* - Interrupt is routed to INT1 pin. */ |

| #define | MMA865x_CTRL_REG5_INT_CFG_LNDPRT_INT2 ((uint8_t) 0x00) /* - Interrupt is routed to INT2 pin. */ |

| #define | MMA865x_CTRL_REG5_INT_CFG_LNDPRT_INT1 ((uint8_t) 0x10) /* - Interrupt is routed to INT1 pin. */ |

| #define | MMA865x_CTRL_REG5_INT_CFG_PULSE_INT2 ((uint8_t) 0x00) /* - Interrupt is routed to INT2 pin. */ |

| #define | MMA865x_CTRL_REG5_INT_CFG_PULSE_INT1 ((uint8_t) 0x08) /* - Interrupt is routed to INT1 pin. */ |

| #define | MMA865x_CTRL_REG5_INT_CFG_FF_MT_INT2 ((uint8_t) 0x00) /* - Interrupt is routed to INT2 pin. */ |

| #define | MMA865x_CTRL_REG5_INT_CFG_FF_MT_INT1 ((uint8_t) 0x04) /* - Interrupt is routed to INT1 pin. */ |

| #define | MMA865x_CTRL_REG5_INT_CFG_DRDY_INT2 ((uint8_t) 0x00) /* - Interrupt is routed to INT2 pin. */ |

| #define | MMA865x_CTRL_REG5_INT_CFG_DRDY_INT1 ((uint8_t) 0x01) /* - Interrupt is routed to INT1 pin. */ |

Typedefs | |

| typedef uint8_t | MMA865x_OUT_X_MSB_t |

| typedef uint8_t | MMA865x_OUT_X_LSB_t |

| typedef uint8_t | MMA865x_OUT_Y_MSB_t |

| typedef uint8_t | MMA865x_OUT_Y_LSB_t |

| typedef uint8_t | MMA865x_OUT_Z_MSB_t |

| typedef uint8_t | MMA865x_OUT_Z_LSB_t |

| typedef uint8_t | MMA865x_WHO_AM_I_t |

| typedef uint8_t | MMA865x_PL_COUNT_t |

| typedef uint8_t | MMA865x_FF_MT_COUNT_t |

| typedef uint8_t | MMA865x_TRANSIENT_COUNT_t |

| typedef uint8_t | MMA865x_PULSE_TMLT_t |

| typedef uint8_t | MMA865x_PULSE_LTCY_t |

| typedef uint8_t | MMA865x_PULSE_WIND_t |

| typedef uint8_t | MMA865x_ASLP_COUNT_t |

| typedef uint8_t | MMA865x_OFF_X_t |

| typedef uint8_t | MMA865x_OFF_Y_t |

| typedef uint8_t | MMA865x_OFF_Z_t |

The mma865x.h contains the MMA865xFC Digital Accelerometer Sensor register definitions, access macros, and device access functions.

Definition in file mma865x.h.

| #define MMA8652_WHOAMI_VALUE (0x4A) /* MMA8652 Who_Am_I Value. */ |

| #define MMA8653_WHOAMI_VALUE (0x5A) /* MMA8653 Who_Am_I Value. */ |

| #define MMA865x_CTRL_REG1_ACTIVE_ACTIVATED ((uint8_t) 0x01) /* - ACTIVE mode. */ |

Definition at line 1559 of file mma865x.h.

Referenced by MMA865x_I2C_Configure().

| #define MMA865x_CTRL_REG1_ACTIVE_MASK ((uint8_t) 0x01) |

Definition at line 1528 of file mma865x.h.

Referenced by MMA865x_I2C_Configure().

| #define MMA865x_CTRL_REG1_ACTIVE_STANDBY ((uint8_t) 0x00) /* - STANDBY mode. */ |

Definition at line 1558 of file mma865x.h.

Referenced by MMA865x_I2C_Configure().

| #define MMA865x_CTRL_REG1_ASLP_RATE_12_5HZ ((uint8_t) 0x40) /* - Frequency = 12.5Hz */ |

| #define MMA865x_CTRL_REG1_ASLP_RATE_1_56HZ ((uint8_t) 0xc0) /* - Frequency = 1.56Hz */ |

| #define MMA865x_CTRL_REG1_ASLP_RATE_50HZ ((uint8_t) 0x00) /* - Frequency = 50Hz */ |

| #define MMA865x_CTRL_REG1_ASLP_RATE_6_25HZ ((uint8_t) 0x80) /* - Frequency = 6.25Hz */ |

| #define MMA865x_CTRL_REG1_ASLP_RATE_MASK ((uint8_t) 0xC0) |

| #define MMA865x_CTRL_REG1_DR_100HZ ((uint8_t) 0x18) /* - ODR = 100Hz. */ |

| #define MMA865x_CTRL_REG1_DR_12_5HZ ((uint8_t) 0x28) /* - ODR = 12.5Hz. */ |

| #define MMA865x_CTRL_REG1_DR_1_56HZ ((uint8_t) 0x38) /* - ODR = 1.56Hz. */ |

| #define MMA865x_CTRL_REG1_DR_200HZ ((uint8_t) 0x10) /* - ODR = 200Hz. */ |

| #define MMA865x_CTRL_REG1_DR_400HZ ((uint8_t) 0x08) /* - ODR = 400Hz. */ |

| #define MMA865x_CTRL_REG1_DR_50HZ ((uint8_t) 0x20) /* - ODR = 50Hz. */ |

| #define MMA865x_CTRL_REG1_DR_6_25HZ ((uint8_t) 0x30) /* - ODR = 6.25Hz. */ |

| #define MMA865x_CTRL_REG1_DR_800HZ ((uint8_t) 0x00) /* - ODR = 800Hz. */ |

| #define MMA865x_CTRL_REG1_F_READ_FAST ((uint8_t) 0x02) /* - Fast Read Mode. */ |

| #define MMA865x_CTRL_REG1_F_READ_NORMAL ((uint8_t) 0x00) /* - Normal Mode. */ |

| #define MMA865x_CTRL_REG2_MODS_HR ((uint8_t) 0x02) /* - High Resolution Mode. */ |

| #define MMA865x_CTRL_REG2_MODS_LNLP ((uint8_t) 0x01) /* - Low Noise Low Power Mode. */ |

| #define MMA865x_CTRL_REG2_MODS_LP ((uint8_t) 0x03) /* - Low Power Mode. */ |

| #define MMA865x_CTRL_REG2_MODS_NORMAL ((uint8_t) 0x00) /* - Normal Mode. */ |

| #define MMA865x_CTRL_REG2_RST_DISABLED ((uint8_t) 0x00) /* - Device reset disabled. */ |

| #define MMA865x_CTRL_REG2_RST_EN ((uint8_t) 0x40) /* - Device reset enabled. */ |

Definition at line 1614 of file mma865x.h.

Referenced by MMA865x_I2C_DeInit().

| #define MMA865x_CTRL_REG2_RST_MASK ((uint8_t) 0x40) |

Definition at line 1601 of file mma865x.h.

Referenced by MMA865x_I2C_DeInit().

| #define MMA865x_CTRL_REG2_SLPE_DISABLED ((uint8_t) 0x00) /* - Auto-SLEEP is not enabled. */ |

| #define MMA865x_CTRL_REG2_SLPE_EN ((uint8_t) 0x04) /* - Auto-SLEEP is enabled. */ |

| #define MMA865x_CTRL_REG2_SMODS_HR ((uint8_t) 0x10) /* - High Resolution Mode. */ |

| #define MMA865x_CTRL_REG2_SMODS_LNLP ((uint8_t) 0x08) /* - Low Noise Low Power Mode. */ |

| #define MMA865x_CTRL_REG2_SMODS_LP ((uint8_t) 0x18) /* - Low Power Mode. */ |

| #define MMA865x_CTRL_REG2_SMODS_NORMAL ((uint8_t) 0x00) /* - Normal Mode. */ |

| #define MMA865x_CTRL_REG2_ST_DISABLED ((uint8_t) 0x00) /* - Self-Test disabled. */ |

| #define MMA865x_CTRL_REG2_ST_EN ((uint8_t) 0x80) /* - Self-Test enabled. */ |

| #define MMA865x_CTRL_REG3_FIFO_GATE_BLOCKED ((uint8_t) 0x80) /* - The FIFO input buffer is blocked when */ |

| #define MMA865x_CTRL_REG3_FIFO_GATE_BYPASSED ((uint8_t) 0x00) /* - FIFO gate is bypassed. */ |

| #define MMA865x_CTRL_REG3_FIFO_GATE_MASK ((uint8_t) 0x80) |

| #define MMA865x_CTRL_REG3_IPOL_ACTIVE_HIGH ((uint8_t) 0x02) /* - ACTIVE high. */ |

| #define MMA865x_CTRL_REG3_IPOL_ACTIVE_LOW ((uint8_t) 0x00) /* - ACTIVE low. */ |

| #define MMA865x_CTRL_REG3_PP_OD_OPEN_DRAIN ((uint8_t) 0x01) /* - Open Drain. */ |

| #define MMA865x_CTRL_REG3_PP_OD_PUSH_PULL ((uint8_t) 0x00) /* - Push-Pull. */ |

| #define MMA865x_CTRL_REG3_WAKE_FF_MT_BYPASSED ((uint8_t) 0x00) /* - Freefall/Motion function is bypassed in SLEEP */ |

| #define MMA865x_CTRL_REG3_WAKE_FF_MT_EN ((uint8_t) 0x08) /* - Freefall/Motion function interrupt can wake up. */ |

| #define MMA865x_CTRL_REG3_WAKE_FF_MT_MASK ((uint8_t) 0x08) |

| #define MMA865x_CTRL_REG3_WAKE_LNDPRT_BYPASSED ((uint8_t) 0x00) /* - Orientation function is bypassed in SLEEP mode. */ |

| #define MMA865x_CTRL_REG3_WAKE_LNDPRT_EN ((uint8_t) 0x20) /* - Orientation function interrupt can wake up */ |

| #define MMA865x_CTRL_REG3_WAKE_LNDPRT_MASK ((uint8_t) 0x20) |

| #define MMA865x_CTRL_REG3_WAKE_LNDPRT_SHIFT ((uint8_t) 5) |

| #define MMA865x_CTRL_REG3_WAKE_PULSE_BYPASSED ((uint8_t) 0x00) /* - Pulse function is bypassed in SLEEP mode. */ |

| #define MMA865x_CTRL_REG3_WAKE_PULSE_EN ((uint8_t) 0x10) /* - Pulse function interrupt can wake up system. */ |

| #define MMA865x_CTRL_REG3_WAKE_PULSE_MASK ((uint8_t) 0x10) |

| #define MMA865x_CTRL_REG3_WAKE_TRANS_BYPASSED ((uint8_t) 0x00) /* - Transient function is bypassed in SLEEP mode. */ |

| #define MMA865x_CTRL_REG3_WAKE_TRANS_EN ((uint8_t) 0x40) /* - Transient function interrupt can wake up system. */ |

| #define MMA865x_CTRL_REG3_WAKE_TRANS_MASK ((uint8_t) 0x40) |

| #define MMA865x_CTRL_REG4_INT_EN_ASLP_DISABLED ((uint8_t) 0x00) /* - Interrupt is disabled. */ |

| #define MMA865x_CTRL_REG4_INT_EN_ASLP_EN ((uint8_t) 0x80) /* - Interrupt is enabled. */ |

| #define MMA865x_CTRL_REG4_INT_EN_ASLP_MASK ((uint8_t) 0x80) |

| #define MMA865x_CTRL_REG4_INT_EN_ASLP_SHIFT ((uint8_t) 7) |

| #define MMA865x_CTRL_REG4_INT_EN_DRDY_DISABLED ((uint8_t) 0x00) /* - Interrupt is disabled. */ |

| #define MMA865x_CTRL_REG4_INT_EN_DRDY_EN ((uint8_t) 0x01) /* - Interrupt is enabled. */ |

| #define MMA865x_CTRL_REG4_INT_EN_DRDY_MASK ((uint8_t) 0x01) |

| #define MMA865x_CTRL_REG4_INT_EN_DRDY_SHIFT ((uint8_t) 0) |

| #define MMA865x_CTRL_REG4_INT_EN_FF_MT_DISABLED ((uint8_t) 0x00) /* - Interrupt is disabled. */ |

| #define MMA865x_CTRL_REG4_INT_EN_FF_MT_EN ((uint8_t) 0x04) /* - Interrupt is enabled. */ |

| #define MMA865x_CTRL_REG4_INT_EN_FF_MT_MASK ((uint8_t) 0x04) |

| #define MMA865x_CTRL_REG4_INT_EN_FF_MT_SHIFT ((uint8_t) 2) |

| #define MMA865x_CTRL_REG4_INT_EN_FIFO_DISABLED ((uint8_t) 0x00) /* - Interrupt is disabled. */ |

| #define MMA865x_CTRL_REG4_INT_EN_FIFO_EN ((uint8_t) 0x40) /* - Interrupt is enabled. */ |

| #define MMA865x_CTRL_REG4_INT_EN_FIFO_MASK ((uint8_t) 0x40) |

| #define MMA865x_CTRL_REG4_INT_EN_FIFO_SHIFT ((uint8_t) 6) |

| #define MMA865x_CTRL_REG4_INT_EN_LNDPRT_DISABLED ((uint8_t) 0x00) /* - Interrupt is disabled. */ |

| #define MMA865x_CTRL_REG4_INT_EN_LNDPRT_EN ((uint8_t) 0x10) /* - Interrupt is enabled. */ |

| #define MMA865x_CTRL_REG4_INT_EN_LNDPRT_MASK ((uint8_t) 0x10) |

| #define MMA865x_CTRL_REG4_INT_EN_LNDPRT_SHIFT ((uint8_t) 4) |

| #define MMA865x_CTRL_REG4_INT_EN_PULSE_DISABLED ((uint8_t) 0x00) /* - Interrupt is disabled. */ |

| #define MMA865x_CTRL_REG4_INT_EN_PULSE_EN ((uint8_t) 0x08) /* - Interrupt is enabled. */ |

| #define MMA865x_CTRL_REG4_INT_EN_PULSE_MASK ((uint8_t) 0x08) |

| #define MMA865x_CTRL_REG4_INT_EN_PULSE_SHIFT ((uint8_t) 3) |

| #define MMA865x_CTRL_REG4_INT_EN_TRANS_DISABLED ((uint8_t) 0x00) /* - Interrupt is disabled. */ |

| #define MMA865x_CTRL_REG4_INT_EN_TRANS_EN ((uint8_t) 0x20) /* - Interrupt is enabled. */ |

| #define MMA865x_CTRL_REG4_INT_EN_TRANS_MASK ((uint8_t) 0x20) |

| #define MMA865x_CTRL_REG4_INT_EN_TRANS_SHIFT ((uint8_t) 5) |

| #define MMA865x_CTRL_REG5_INT_CFG_ASLP_INT1 ((uint8_t) 0x80) /* - Interrupt is routed to INT1 pin. */ |

| #define MMA865x_CTRL_REG5_INT_CFG_ASLP_INT2 ((uint8_t) 0x00) /* - Interrupt is routed to INT2 pin. */ |

| #define MMA865x_CTRL_REG5_INT_CFG_ASLP_MASK ((uint8_t) 0x80) |

| #define MMA865x_CTRL_REG5_INT_CFG_ASLP_SHIFT ((uint8_t) 7) |

| #define MMA865x_CTRL_REG5_INT_CFG_DRDY_INT1 ((uint8_t) 0x01) /* - Interrupt is routed to INT1 pin. */ |

| #define MMA865x_CTRL_REG5_INT_CFG_DRDY_INT2 ((uint8_t) 0x00) /* - Interrupt is routed to INT2 pin. */ |

| #define MMA865x_CTRL_REG5_INT_CFG_DRDY_MASK ((uint8_t) 0x01) |

| #define MMA865x_CTRL_REG5_INT_CFG_DRDY_SHIFT ((uint8_t) 0) |

| #define MMA865x_CTRL_REG5_INT_CFG_FF_MT_INT1 ((uint8_t) 0x04) /* - Interrupt is routed to INT1 pin. */ |

| #define MMA865x_CTRL_REG5_INT_CFG_FF_MT_INT2 ((uint8_t) 0x00) /* - Interrupt is routed to INT2 pin. */ |

| #define MMA865x_CTRL_REG5_INT_CFG_FF_MT_MASK ((uint8_t) 0x04) |

| #define MMA865x_CTRL_REG5_INT_CFG_FF_MT_SHIFT ((uint8_t) 2) |

| #define MMA865x_CTRL_REG5_INT_CFG_FIFO_INT1 ((uint8_t) 0x40) /* - Interrupt is routed to INT1 pin. */ |

| #define MMA865x_CTRL_REG5_INT_CFG_FIFO_INT2 ((uint8_t) 0x00) /* - Interrupt is routed to INT2 pin. */ |

| #define MMA865x_CTRL_REG5_INT_CFG_FIFO_MASK ((uint8_t) 0x40) |

| #define MMA865x_CTRL_REG5_INT_CFG_FIFO_SHIFT ((uint8_t) 6) |

| #define MMA865x_CTRL_REG5_INT_CFG_LNDPRT_INT1 ((uint8_t) 0x10) /* - Interrupt is routed to INT1 pin. */ |

| #define MMA865x_CTRL_REG5_INT_CFG_LNDPRT_INT2 ((uint8_t) 0x00) /* - Interrupt is routed to INT2 pin. */ |

| #define MMA865x_CTRL_REG5_INT_CFG_LNDPRT_MASK ((uint8_t) 0x10) |

| #define MMA865x_CTRL_REG5_INT_CFG_LNDPRT_SHIFT ((uint8_t) 4) |

| #define MMA865x_CTRL_REG5_INT_CFG_PULSE_INT1 ((uint8_t) 0x08) /* - Interrupt is routed to INT1 pin. */ |

| #define MMA865x_CTRL_REG5_INT_CFG_PULSE_INT2 ((uint8_t) 0x00) /* - Interrupt is routed to INT2 pin. */ |

| #define MMA865x_CTRL_REG5_INT_CFG_PULSE_MASK ((uint8_t) 0x08) |

| #define MMA865x_CTRL_REG5_INT_CFG_PULSE_SHIFT ((uint8_t) 3) |

| #define MMA865x_CTRL_REG5_INT_CFG_TRANS_INT1 ((uint8_t) 0x20) /* - Interrupt is routed to INT1 pin. */ |

| #define MMA865x_CTRL_REG5_INT_CFG_TRANS_INT2 ((uint8_t) 0x00) /* - Interrupt is routed to INT2 pin. */ |

| #define MMA865x_CTRL_REG5_INT_CFG_TRANS_MASK ((uint8_t) 0x20) |

| #define MMA865x_CTRL_REG5_INT_CFG_TRANS_SHIFT ((uint8_t) 5) |

| #define MMA865x_F_SETUP_F_MODE_CIR_MODE ((uint8_t) 0x40) /* - FIFO is in Circular Buffer mode. */ |

| #define MMA865x_F_SETUP_F_MODE_FIFO_OFF ((uint8_t) 0x00) /* - FIFO is disabled. */ |

| #define MMA865x_F_SETUP_F_MODE_STOP_MODE ((uint8_t) 0x80) /* - FIFO is in Stop mode. */ |

| #define MMA865x_F_SETUP_F_MODE_TRIG_MODE ((uint8_t) 0xc0) /* - FIFO is in Trigger mode. The FIFO will be in a */ |

| #define MMA865x_F_STATUS_F_OVF_DETECTED ((uint8_t) 0x80) /* - FIFO Overflow event has been detected. */ |

| #define MMA865x_F_STATUS_F_OVF_NONE ((uint8_t) 0x00) /* - FIFO Overflow event has NOT been detected. */ |

| #define MMA865x_F_STATUS_F_WMKF_DETECTED ((uint8_t) 0x40) /* - FIFO Watermark event has been detected. */ |

| #define MMA865x_F_STATUS_F_WMKF_MASK ((uint8_t) 0x40) |

| #define MMA865x_F_STATUS_F_WMKF_NONE ((uint8_t) 0x00) /* - FIFO Watermark event has NOT been detected. */ |

| #define MMA865x_FF_MT_CFG_ELE_DISABLED ((uint8_t) 0x00) /* - Event flag latch disabled. */ |

| #define MMA865x_FF_MT_CFG_ELE_EN ((uint8_t) 0x80) /* - Event flag latch enabled. */ |

| #define MMA865x_FF_MT_CFG_OAE_FREEFALL ((uint8_t) 0x00) /* - Freefall flag (Logical AND combination). */ |

| #define MMA865x_FF_MT_CFG_OAE_MOTION ((uint8_t) 0x40) /* - Motion flag (Logical OR combination). */ |

| #define MMA865x_FF_MT_CFG_XEFE_DISABLED ((uint8_t) 0x00) /* - Event detection disabled. */ |

| #define MMA865x_FF_MT_CFG_XEFE_EN ((uint8_t) 0x08) /* - Raise event flag on measured acceleration value */ |

| #define MMA865x_FF_MT_CFG_YEFE_DISABLED ((uint8_t) 0x00) /* - Event detection disabled. */ |

| #define MMA865x_FF_MT_CFG_YEFE_EN ((uint8_t) 0x10) /* - Raise event flag on measured acceleration value */ |

| #define MMA865x_FF_MT_CFG_ZEFE_DISABLED ((uint8_t) 0x00) /* - Event detection disabled. */ |

| #define MMA865x_FF_MT_CFG_ZEFE_EN ((uint8_t) 0x20) /* - Raise event flag on measured acceleration value */ |

| #define MMA865x_FF_MT_SRC_EA_DETECTED ((uint8_t) 0x80) /* - One or more event flags has been asserted. */ |

| #define MMA865x_FF_MT_SRC_EA_MASK ((uint8_t) 0x80) |

| #define MMA865x_FF_MT_SRC_EA_NONE ((uint8_t) 0x00) /* - No event flag has been asserted. */ |

| #define MMA865x_FF_MT_SRC_XHE_DETECTED ((uint8_t) 0x02) /* - X motion has been detected. */ |

| #define MMA865x_FF_MT_SRC_XHE_NONE ((uint8_t) 0x00) /* - No X motion event detected. */ |

| #define MMA865x_FF_MT_SRC_XHP_NEGATIVE ((uint8_t) 0x01) /* - X event was negative g. */ |

| #define MMA865x_FF_MT_SRC_XHP_POSITIVE ((uint8_t) 0x00) /* - X event was positive g. */ |

| #define MMA865x_FF_MT_SRC_YHE_DETECTED ((uint8_t) 0x08) /* - Y motion has been detected. */ |

| #define MMA865x_FF_MT_SRC_YHE_NONE ((uint8_t) 0x00) /* - No Y motion event detected. */ |

| #define MMA865x_FF_MT_SRC_YHP_NEGATIVE ((uint8_t) 0x04) /* - Y event was negative g. */ |

| #define MMA865x_FF_MT_SRC_YHP_POSITIVE ((uint8_t) 0x00) /* - Y event detected was positive g. */ |

| #define MMA865x_FF_MT_SRC_ZHE_DETECTED ((uint8_t) 0x20) /* - Z motion has been detected. */ |

| #define MMA865x_FF_MT_SRC_ZHE_NONE ((uint8_t) 0x00) /* - No Z motion event detected. */ |

| #define MMA865x_FF_MT_SRC_ZHP_NEGATIVE ((uint8_t) 0x10) /* - Z event was negative g. */ |

| #define MMA865x_FF_MT_SRC_ZHP_POSITIVE ((uint8_t) 0x00) /* - Z event was positive g. */ |

| #define MMA865x_FF_MT_THS_DBCNTM_INC_CLR ((uint8_t) 0x80) /* - Increments or clears counter. */ |

| #define MMA865x_FF_MT_THS_DBCNTM_INC_DEC ((uint8_t) 0x00) /* - Increments or decrements debounce. */ |

| #define MMA865x_HP_FILTER_CUTOFF_PULSE_HPF_BYP_BYPASSED ((uint8_t) 0x20) /* - HPF is bypassed for pulse processing. */ |

| #define MMA865x_HP_FILTER_CUTOFF_PULSE_HPF_BYP_ENABLED ((uint8_t) 0x00) /* - HPF is enabled for pulse processing. */ |

| #define MMA865x_HP_FILTER_CUTOFF_PULSE_HPF_BYP_MASK ((uint8_t) 0x20) |

| #define MMA865x_HP_FILTER_CUTOFF_PULSE_HPF_BYP_SHIFT ((uint8_t) 5) |

| #define MMA865x_HP_FILTER_CUTOFF_PULSE_LPF_EN_DISABLED ((uint8_t) 0x00) /* - LPF is disabled for pulse processing. */ |

| #define MMA865x_HP_FILTER_CUTOFF_PULSE_LPF_EN_ENABLED ((uint8_t) 0x10) /* - LPF is enabled for pulse processing. */ |

| #define MMA865x_HP_FILTER_CUTOFF_PULSE_LPF_EN_MASK ((uint8_t) 0x10) |

| #define MMA865x_HP_FILTER_CUTOFF_PULSE_LPF_EN_SHIFT ((uint8_t) 4) |

| #define MMA865x_HP_FILTER_CUTOFF_SEL_MASK ((uint8_t) 0x03) |

| #define MMA865x_HP_FILTER_CUTOFF_SEL_VAL_0 ((uint8_t) 0x00) /* - Select 0 0 */ |

| #define MMA865x_HP_FILTER_CUTOFF_SEL_VAL_1 ((uint8_t) 0x00) /* - Select 0 1 */ |

| #define MMA865x_HP_FILTER_CUTOFF_SEL_VAL_2 ((uint8_t) 0x00) /* - Select 1 0 */ |

| #define MMA865x_HP_FILTER_CUTOFF_SEL_VAL_3 ((uint8_t) 0x00) /* - Select 1 1 */ |

| #define MMA865x_I2C_ADDRESS (0x1D) /* MMA865x I2C Slave Address. */ |

| #define MMA865x_INT_SOURCE_SRC_ASLP_INACTIVE ((uint8_t) 0x00) /* - No WAKE-to-SLEEP or SLEEP-to-WAKE system mode */ |

| #define MMA865x_INT_SOURCE_SRC_ASLP_MASK ((uint8_t) 0x80) |

| #define MMA865x_INT_SOURCE_SRC_ASLP_READY ((uint8_t) 0x80) /* - An interrupt event that can cause a */ |

| #define MMA865x_INT_SOURCE_SRC_DRDY_INACTIVE ((uint8_t) 0x00) /* - The X, Y, Z interrupt is not active. */ |

| #define MMA865x_INT_SOURCE_SRC_DRDY_READY ((uint8_t) 0x01) /* - The X, Y, Z data ready interrupt is active. */ |

| #define MMA865x_INT_SOURCE_SRC_FF_MT_INACTIVE ((uint8_t) 0x00) /* - No Freefall or Motion event was detected. */ |

| #define MMA865x_INT_SOURCE_SRC_FF_MT_MASK ((uint8_t) 0x04) |

| #define MMA865x_INT_SOURCE_SRC_FF_MT_READY ((uint8_t) 0x04) /* - The Freefall/Motion function interrupt is */ |

| #define MMA865x_INT_SOURCE_SRC_FIFO_INACTIVE ((uint8_t) 0x00) /* - No FIFO interrupt event has occurred. */ |

| #define MMA865x_INT_SOURCE_SRC_FIFO_READY ((uint8_t) 0x40) /* - A FIFO interrupt event (such as an overflow */ |

| #define MMA865x_INT_SOURCE_SRC_LNDPRT_INACTIVE ((uint8_t) 0x00) /* - No change in orientation status was detected. */ |

| #define MMA865x_INT_SOURCE_SRC_LNDPRT_MASK ((uint8_t) 0x10) |

| #define MMA865x_INT_SOURCE_SRC_LNDPRT_READY ((uint8_t) 0x10) /* - An interrupt was generated due to a change in */ |

| #define MMA865x_INT_SOURCE_SRC_PULSE_INACTIVE ((uint8_t) 0x00) /* - No pulse event was detected. */ |

| #define MMA865x_INT_SOURCE_SRC_PULSE_MASK ((uint8_t) 0x08) |

| #define MMA865x_INT_SOURCE_SRC_PULSE_READY ((uint8_t) 0x08) /* - An interrupt was generated due to single and/or */ |

| #define MMA865x_INT_SOURCE_SRC_TRANS_INACTIVE ((uint8_t) 0x00) /* - No transient event has occurred. */ |

| #define MMA865x_INT_SOURCE_SRC_TRANS_MASK ((uint8_t) 0x20) |

| #define MMA865x_INT_SOURCE_SRC_TRANS_READY ((uint8_t) 0x20) /* - An acceleration transient value greater than */ |

| #define MMA865x_P_L_THS_REG_HYS_VAL_0 ((uint8_t) 0x00) /* - Hysteresis � Angle Range = �0 */ |

| #define MMA865x_P_L_THS_REG_HYS_VAL_1 ((uint8_t) 0x01) /* - Hysteresis � Angle Range = �4 */ |

| #define MMA865x_P_L_THS_REG_HYS_VAL_2 ((uint8_t) 0x02) /* - Hysteresis � Angle Range = �7 */ |

| #define MMA865x_P_L_THS_REG_HYS_VAL_3 ((uint8_t) 0x03) /* - Hysteresis � Angle Range = �11 */ |

| #define MMA865x_P_L_THS_REG_HYS_VAL_4 ((uint8_t) 0x04) /* - Hysteresis � Angle Range = �14 */ |

| #define MMA865x_P_L_THS_REG_HYS_VAL_5 ((uint8_t) 0x05) /* - Hysteresis � Angle Range = �17 */ |

| #define MMA865x_P_L_THS_REG_HYS_VAL_6 ((uint8_t) 0x06) /* - Hysteresis � Angle Range = �21 */ |

| #define MMA865x_P_L_THS_REG_HYS_VAL_7 ((uint8_t) 0x07) /* - Hysteresis � Angle Range = �24 */ |

| #define MMA865x_P_L_THS_REG_P_L_THS_VAL_15 ((uint8_t) 0x38) /* - Threshold Angle = 15� */ |

| #define MMA865x_P_L_THS_REG_P_L_THS_VAL_20 ((uint8_t) 0x48) /* - Threshold Angle = 20� */ |

| #define MMA865x_P_L_THS_REG_P_L_THS_VAL_30 ((uint8_t) 0x60) /* - Threshold Angle = 30� */ |

| #define MMA865x_P_L_THS_REG_P_L_THS_VAL_35 ((uint8_t) 0x68) /* - Threshold Angle = 35� */ |

| #define MMA865x_P_L_THS_REG_P_L_THS_VAL_40 ((uint8_t) 0x78) /* - Threshold Angle = 40� */ |

| #define MMA865x_P_L_THS_REG_P_L_THS_VAL_45 ((uint8_t) 0x80) /* - Threshold Angle = 45� */ |

| #define MMA865x_P_L_THS_REG_P_L_THS_VAL_55 ((uint8_t) 0x98) /* - Threshold Angle = 55� */ |

| #define MMA865x_P_L_THS_REG_P_L_THS_VAL_60 ((uint8_t) 0xa0) /* - Threshold Angle = 60� */ |

| #define MMA865x_P_L_THS_REG_P_L_THS_VAL_70 ((uint8_t) 0xb8) /* - Threshold Angle = 70� */ |

| #define MMA865x_P_L_THS_REG_P_L_THS_VAL_75 ((uint8_t) 0xc8) /* - Threshold Angle = 75� */ |

| #define MMA865x_PL_BF_ZCOMP_BKFR_VAL_0 ((uint8_t) 0x00) /* - Back/Front Transition : 00 Z < 80� or Z > 280� */ |

| #define MMA865x_PL_BF_ZCOMP_BKFR_VAL_1 ((uint8_t) 0x40) /* - Back/Front Transition : 01 Z < 75� or Z > 285� */ |

| #define MMA865x_PL_BF_ZCOMP_BKFR_VAL_2 ((uint8_t) 0x80) /* - Back/Front Transition : 10 Z < 70� or Z > 290� */ |

| #define MMA865x_PL_BF_ZCOMP_BKFR_VAL_3 ((uint8_t) 0xc0) /* - Back/Front Transition : 11 Z < 65� or Z > 295� */ |

| #define MMA865x_PL_BF_ZCOMP_ZLOCK_VAL_14 ((uint8_t) 0x00) /* - Threshold Angle = 14�. */ |

| #define MMA865x_PL_BF_ZCOMP_ZLOCK_VAL_18 ((uint8_t) 0x01) /* - Threshold Angle = 18�. */ |

| #define MMA865x_PL_BF_ZCOMP_ZLOCK_VAL_21 ((uint8_t) 0x02) /* - Threshold Angle = 21�. */ |

| #define MMA865x_PL_BF_ZCOMP_ZLOCK_VAL_25 ((uint8_t) 0x03) /* - Threshold Angle = 25�. */ |

| #define MMA865x_PL_BF_ZCOMP_ZLOCK_VAL_29 ((uint8_t) 0x04) /* - Threshold Angle = 29�. */ |

| #define MMA865x_PL_BF_ZCOMP_ZLOCK_VAL_33 ((uint8_t) 0x05) /* - Threshold Angle = 33�. */ |

| #define MMA865x_PL_BF_ZCOMP_ZLOCK_VAL_37 ((uint8_t) 0x06) /* - Threshold Angle = 37�. */ |

| #define MMA865x_PL_BF_ZCOMP_ZLOCK_VAL_42 ((uint8_t) 0x07) /* - Threshold Angle = 42�. */ |

| #define MMA865x_PL_CFG_DBCNTM_CLEAR ((uint8_t) 0x80) /* - Clears the counter whenever the condition of */ |

| #define MMA865x_PL_CFG_DBCNTM_DECREMENT ((uint8_t) 0x00) /* - Decrements debounce whenever the condition of */ |

| #define MMA865x_PL_CFG_PL_EN_DISABLED ((uint8_t) 0x00) /* - Portrait/Landscape Detection is disabled. */ |

| #define MMA865x_PL_CFG_PL_EN_EN ((uint8_t) 0x40) /* - Portrait/Landscape Detection is enabled. */ |

| #define MMA865x_PL_STATUS_BAFRO_BACK ((uint8_t) 0x01) /* - Back: Equipment is in the back-facing */ |

| #define MMA865x_PL_STATUS_BAFRO_FRONT ((uint8_t) 0x00) /* - Front: Equipment is in the front-facing */ |

| #define MMA865x_PL_STATUS_LAPO_LANDSCAPE_DOWN ((uint8_t) 0x06) /* - Landscape Left: Equipment is in landscape mode to */ |

| #define MMA865x_PL_STATUS_LAPO_LANDSCAPE_UP ((uint8_t) 0x04) /* - Landscape Right: Equipment is in landscape mode */ |

| #define MMA865x_PL_STATUS_LAPO_PORTRAIT_DOWN ((uint8_t) 0x02) /* - Portrait Down: Equipment standing vertically in */ |

| #define MMA865x_PL_STATUS_LAPO_PORTRAIT_UP ((uint8_t) 0x00) /* - Portrait Up: Equipment standing vertically in the */ |

| #define MMA865x_PL_STATUS_LO_DETECTED ((uint8_t) 0x40) /* - Z-Tilt lockout trip angle has been exceeded. */ |

| #define MMA865x_PL_STATUS_LO_NOT_DETECTED ((uint8_t) 0x00) /* - Lockout condition has not been detected. */ |

| #define MMA865x_PL_STATUS_NEWLP_DETECTED ((uint8_t) 0x80) /* - BAFRO and/or LAPO and/or Z-Tilt lockout value has */ |

| #define MMA865x_PL_STATUS_NEWLP_NO_CHANGE ((uint8_t) 0x00) /* - No change. */ |

| #define MMA865x_PULSE_CFG_DPA_NOT_ABORTED ((uint8_t) 0x00) /* - Double Pulse detection is not aborted if the */ |

| #define MMA865x_PULSE_CFG_DPA_SUSPENDED ((uint8_t) 0x80) /* - Setting the DPA bit momentarily suspends the */ |

| #define MMA865x_PULSE_CFG_ELE_DISABLED ((uint8_t) 0x00) /* - Event detection is disabled. */ |

| #define MMA865x_PULSE_CFG_ELE_EN ((uint8_t) 0x40) /* - Event detection is enabled. */ |

| #define MMA865x_PULSE_CFG_XDPEFE_DISABLED ((uint8_t) 0x00) /* - Event detection is disabled. */ |

| #define MMA865x_PULSE_CFG_XDPEFE_EN ((uint8_t) 0x02) /* - Event detection is enabled. */ |

| #define MMA865x_PULSE_CFG_XSPEFE_DISABLED ((uint8_t) 0x00) /* - Event detection is disabled. */ |

| #define MMA865x_PULSE_CFG_XSPEFE_EN ((uint8_t) 0x01) /* - Event detection is enabled. */ |

| #define MMA865x_PULSE_CFG_YDPEFE_DISABLED ((uint8_t) 0x00) /* - Event detection is disabled. */ |

| #define MMA865x_PULSE_CFG_YDPEFE_EN ((uint8_t) 0x08) /* - Event detection is enabled. */ |

| #define MMA865x_PULSE_CFG_YSPEFE_DISABLED ((uint8_t) 0x00) /* - Event detection is disabled. */ |

| #define MMA865x_PULSE_CFG_YSPEFE_EN ((uint8_t) 0x04) /* - Event detection is enabled. */ |

| #define MMA865x_PULSE_CFG_ZDPEFE_DISABLED ((uint8_t) 0x00) /* - Event detection is disabled. */ |

| #define MMA865x_PULSE_CFG_ZDPEFE_EN ((uint8_t) 0x20) /* - Event detection is enabled. */ |

| #define MMA865x_PULSE_CFG_ZSPEFE_DISABLED ((uint8_t) 0x00) /* - Event detection is disabled. */ |

| #define MMA865x_PULSE_CFG_ZSPEFE_EN ((uint8_t) 0x10) /* - Event detection is enabled. */ |

| #define MMA865x_PULSE_SRC_AXX_DETECTED ((uint8_t) 0x10) /* - X-axis event has occurred. */ |

| #define MMA865x_PULSE_SRC_AXX_NONE ((uint8_t) 0x00) /* - No interrupt. */ |

| #define MMA865x_PULSE_SRC_AXY_DETECTED ((uint8_t) 0x20) /* - Y-axis event has occurred. */ |

| #define MMA865x_PULSE_SRC_AXY_NONE ((uint8_t) 0x00) /* - No interrupt. */ |

| #define MMA865x_PULSE_SRC_AXZ_DETECTED ((uint8_t) 0x40) /* - Z-axis event has occurred. */ |

| #define MMA865x_PULSE_SRC_AXZ_NONE ((uint8_t) 0x00) /* - No interrupt. */ |

| #define MMA865x_PULSE_SRC_DPE_DOUBLE ((uint8_t) 0x08) /* - Double pulse event triggered interrupt. */ |

| #define MMA865x_PULSE_SRC_DPE_SINGLE ((uint8_t) 0x00) /* - Single pulse event triggered interrupt. */ |

| #define MMA865x_PULSE_SRC_EA_DETECTED ((uint8_t) 0x80) /* - One or more interrupt events have been generated. */ |

| #define MMA865x_PULSE_SRC_EA_NONE ((uint8_t) 0x00) /* - No interrupt has been generated. */ |

| #define MMA865x_PULSE_SRC_POL_X_NEGATIVE ((uint8_t) 0x01) /* - Pulse event that triggered interrupt was */ |

| #define MMA865x_PULSE_SRC_POL_X_POSITIVE ((uint8_t) 0x00) /* - Pulse event that triggered interrupt was */ |

| #define MMA865x_PULSE_SRC_POL_Y_NEGATIVE ((uint8_t) 0x02) /* - Pulse event that triggered interrupt was */ |

| #define MMA865x_PULSE_SRC_POL_Y_POSITIVE ((uint8_t) 0x00) /* - Pulse event that triggered interrupt was */ |

| #define MMA865x_PULSE_SRC_POL_Z_NEGATIVE ((uint8_t) 0x04) /* - Pulse event that triggered interrupt was */ |

| #define MMA865x_PULSE_SRC_POL_Z_POSITIVE ((uint8_t) 0x00) /* - Pulse event that triggered interrupt was */ |

| #define MMA865x_STATUS_XDR_DRDY ((uint8_t) 0x01) /* - Set to 1 whenever new X-axis data acquisition is */ |

| #define MMA865x_STATUS_XOW_OWR ((uint8_t) 0x10) /* - Set to 1 whenever new X-axis acquisition is */ |

| #define MMA865x_STATUS_YDR_DRDY ((uint8_t) 0x02) /* - Set to 1 whenever new Y-axis data acquisition is */ |

| #define MMA865x_STATUS_YOW_OWR ((uint8_t) 0x20) /* - Set to 1 whenever new Y-axis acquisition is */ |

| #define MMA865x_STATUS_ZDR_DRDY ((uint8_t) 0x04) /* - Set to 1 whenever new Z-axis data acquisition is */ |

| #define MMA865x_STATUS_ZOW_OWR ((uint8_t) 0x40) /* - Set to 1 whenever new Z-axis acquisition is */ |

| #define MMA865x_STATUS_ZYXDR_DRDY ((uint8_t) 0x08) /* - Signals that new acquisition for any of the enabled */ |

| #define MMA865x_STATUS_ZYXDR_MASK ((uint8_t) 0x08) |

| #define MMA865x_STATUS_ZYXOW_OWR ((uint8_t) 0x80) /* - Set to 1 whenever new data is acquired before */ |

| #define MMA865x_SYSMOD_FGERR_DETECTED ((uint8_t) 0x80) /* - FIFO Gate Error was detected. */ |

| #define MMA865x_SYSMOD_FGERR_NONE ((uint8_t) 0x00) /* - No FIFO Gate Error detected. */ |

| #define MMA865x_SYSMOD_SYSMOD_SLEEP ((uint8_t) 0x02) /* - SLEEP Mode. */ |

| #define MMA865x_SYSMOD_SYSMOD_STANDBY ((uint8_t) 0x00) /* - STANDBY Mode. */ |

| #define MMA865x_SYSMOD_SYSMOD_WAKE ((uint8_t) 0x01) /* - WAKE Mode. */ |

| #define MMA865x_TRANSIENT_CFG_ELE_DISABLED ((uint8_t) 0x00) /* - Event flag latch disabled. */ |

| #define MMA865x_TRANSIENT_CFG_ELE_EN ((uint8_t) 0x10) /* - Event flag latch enabled. */ |

| #define MMA865x_TRANSIENT_CFG_HPF_BYP_MASK ((uint8_t) 0x01) |

| #define MMA865x_TRANSIENT_CFG_HPF_BYP_NOT_HPF ((uint8_t) 0x01) /* - Data to transient acceleration detection */ |

| #define MMA865x_TRANSIENT_CFG_HPF_BYP_SHIFT ((uint8_t) 0) |

| #define MMA865x_TRANSIENT_CFG_HPF_BYP_THROUGH_HPF ((uint8_t) 0x00) /* - Data to transient acceleration detection */ |

| #define MMA865x_TRANSIENT_CFG_XTEFE_DISABLED ((uint8_t) 0x00) /* - Event detection disabled. */ |

| #define MMA865x_TRANSIENT_CFG_XTEFE_EN ((uint8_t) 0x02) /* - Raise event flag on measured acceleration */ |

| #define MMA865x_TRANSIENT_CFG_XTEFE_MASK ((uint8_t) 0x02) |

| #define MMA865x_TRANSIENT_CFG_YTEFE_DISABLED ((uint8_t) 0x00) /* - Event detection disabled. */ |

| #define MMA865x_TRANSIENT_CFG_YTEFE_EN ((uint8_t) 0x04) /* - Raise event flag on measured acceleration */ |

| #define MMA865x_TRANSIENT_CFG_YTEFE_MASK ((uint8_t) 0x04) |

| #define MMA865x_TRANSIENT_CFG_ZTEFE_DISABLED ((uint8_t) 0x00) /* - Event detection disabled. */ |

| #define MMA865x_TRANSIENT_CFG_ZTEFE_EN ((uint8_t) 0x08) /* - Raise event flag on measured acceleration */ |

| #define MMA865x_TRANSIENT_CFG_ZTEFE_MASK ((uint8_t) 0x08) |

| #define MMA865x_TRANSIENT_SRC_EA_DETECTED ((uint8_t) 0x40) /* - One or more event flags has been asserted. */ |

| #define MMA865x_TRANSIENT_SRC_EA_NONE ((uint8_t) 0x00) /* - No event flag has been asserted. */ |

| #define MMA865x_TRANSIENT_SRC_X_TRANS_POL_MASK ((uint8_t) 0x01) |

| #define MMA865x_TRANSIENT_SRC_X_TRANS_POL_NEGATIVE ((uint8_t) 0x01) /* - X-event was Negative g. */ |

| #define MMA865x_TRANSIENT_SRC_X_TRANS_POL_POSITIVE ((uint8_t) 0x00) /* - X-event was Positive g. */ |

| #define MMA865x_TRANSIENT_SRC_X_TRANS_POL_SHIFT ((uint8_t) 0) |

| #define MMA865x_TRANSIENT_SRC_XTRANSE_DETECTED ((uint8_t) 0x02) /* - X-transient acceleration greater than the */ |

| #define MMA865x_TRANSIENT_SRC_XTRANSE_MASK ((uint8_t) 0x02) |

| #define MMA865x_TRANSIENT_SRC_XTRANSE_NONE ((uint8_t) 0x00) /* - No interrupt. */ |

| #define MMA865x_TRANSIENT_SRC_XTRANSE_SHIFT ((uint8_t) 1) |

| #define MMA865x_TRANSIENT_SRC_Y_TRANS_POL_MASK ((uint8_t) 0x04) |

| #define MMA865x_TRANSIENT_SRC_Y_TRANS_POL_NEGATIVE ((uint8_t) 0x04) /* - Y-event was Negative g. */ |

| #define MMA865x_TRANSIENT_SRC_Y_TRANS_POL_POSITIVE ((uint8_t) 0x00) /* - Y-event was Positive g. */ |

| #define MMA865x_TRANSIENT_SRC_Y_TRANS_POL_SHIFT ((uint8_t) 2) |

| #define MMA865x_TRANSIENT_SRC_YTRANSE_DETECTED ((uint8_t) 0x08) /* - Y-transient acceleration greater than the */ |

| #define MMA865x_TRANSIENT_SRC_YTRANSE_MASK ((uint8_t) 0x08) |

| #define MMA865x_TRANSIENT_SRC_YTRANSE_NONE ((uint8_t) 0x00) /* - No interrupt. */ |

| #define MMA865x_TRANSIENT_SRC_YTRANSE_SHIFT ((uint8_t) 3) |

| #define MMA865x_TRANSIENT_SRC_Z_TRANS_POL_MASK ((uint8_t) 0x10) |

| #define MMA865x_TRANSIENT_SRC_Z_TRANS_POL_NEGATIVE ((uint8_t) 0x10) /* - Z-event was negative g. */ |

| #define MMA865x_TRANSIENT_SRC_Z_TRANS_POL_POSITIVE ((uint8_t) 0x00) /* - Z-event was positive g. */ |

| #define MMA865x_TRANSIENT_SRC_Z_TRANS_POL_SHIFT ((uint8_t) 4) |

| #define MMA865x_TRANSIENT_SRC_ZTRANSE_DETECTED ((uint8_t) 0x20) /* - Z-transient acceleration greater than the */ |

| #define MMA865x_TRANSIENT_SRC_ZTRANSE_MASK ((uint8_t) 0x20) |

| #define MMA865x_TRANSIENT_SRC_ZTRANSE_NONE ((uint8_t) 0x00) /* - No interrupt. */ |

| #define MMA865x_TRANSIENT_SRC_ZTRANSE_SHIFT ((uint8_t) 5) |

| #define MMA865x_TRANSIENT_THS_DBCNTM_INC_CLR ((uint8_t) 0x80) /* - Increments or clears counter. */ |

| #define MMA865x_TRANSIENT_THS_DBCNTM_INC_DEC ((uint8_t) 0x00) /* - Increments or decrements debounce. */ |

| #define MMA865x_TRANSIENT_THS_DBCNTM_MASK ((uint8_t) 0x80) |

| #define MMA865x_TRIG_CFG_TRIG_FF_MT_DISABLED ((uint8_t) 0x00) /* - This function has not asserted its interrupt. */ |

| #define MMA865x_TRIG_CFG_TRIG_FF_MT_EN ((uint8_t) 0x04) /* - This function can trigger the FIFO at its (the */ |

| #define MMA865x_TRIG_CFG_TRIG_LNDPRT_DISABLED ((uint8_t) 0x00) /* - This function has not asserted its interrupt. */ |

| #define MMA865x_TRIG_CFG_TRIG_LNDPRT_EN ((uint8_t) 0x10) /* - This function can trigger the FIFO at its (the */ |

| #define MMA865x_TRIG_CFG_TRIG_LNDPRT_MASK ((uint8_t) 0x10) |

| #define MMA865x_TRIG_CFG_TRIG_PULSE_DISABLED ((uint8_t) 0x00) /* - This function has not asserted its interrupt. */ |

| #define MMA865x_TRIG_CFG_TRIG_PULSE_EN ((uint8_t) 0x08) /* - This function can trigger the FIFO at its (the */ |

| #define MMA865x_TRIG_CFG_TRIG_TRANS_DISABLED ((uint8_t) 0x00) /* - This function has not asserted its interrupt. */ |

| #define MMA865x_TRIG_CFG_TRIG_TRANS_EN ((uint8_t) 0x20) /* - This function can trigger the FIFO at its (the */ |

| #define MMA865x_XYZ_DATA_CFG_FS_2G ((uint8_t) 0x00) /* - �2 g. */ |

| #define MMA865x_XYZ_DATA_CFG_FS_4G ((uint8_t) 0x01) /* - �4 g. */ |

| #define MMA865x_XYZ_DATA_CFG_FS_8G ((uint8_t) 0x02) /* - �8 g. */ |

| #define MMA865x_XYZ_DATA_CFG_HPF_OUT_DISABLE ((uint8_t) 0x00) /* - Output data is not high-pass filtered. */ |

| #define MMA865x_XYZ_DATA_CFG_HPF_OUT_ENABLE ((uint8_t) 0x10) /* - Output data is high-pass filtered. */ |

| #define MMA865x_XYZ_DATA_CFG_HPF_OUT_MASK ((uint8_t) 0x10) |

| typedef uint8_t MMA865x_ASLP_COUNT_t |

| typedef uint8_t MMA865x_FF_MT_COUNT_t |

| typedef uint8_t MMA865x_OFF_X_t |

| typedef uint8_t MMA865x_OFF_Y_t |

| typedef uint8_t MMA865x_OFF_Z_t |

| typedef uint8_t MMA865x_OUT_X_LSB_t |

| typedef uint8_t MMA865x_OUT_X_MSB_t |

| typedef uint8_t MMA865x_OUT_Y_LSB_t |

| typedef uint8_t MMA865x_OUT_Y_MSB_t |

| typedef uint8_t MMA865x_OUT_Z_LSB_t |

| typedef uint8_t MMA865x_OUT_Z_MSB_t |

| typedef uint8_t MMA865x_PL_COUNT_t |

| typedef uint8_t MMA865x_PULSE_LTCY_t |

| typedef uint8_t MMA865x_PULSE_TMLT_t |

| typedef uint8_t MMA865x_PULSE_WIND_t |

| typedef uint8_t MMA865x_TRANSIENT_COUNT_t |

| typedef uint8_t MMA865x_WHO_AM_I_t |

| anonymous enum |

MMA865x Sensor Internal Registers